the relevance of the developed mathematical model for studying the processes of signals sampling in presence of timing jitter. The model plays major role for the analytical study and description of the problem given in [1].

3. The proposed algorithm helps the easy application of the method wherever the timing jitter causes problems with the accuracy, stability and statistics of the signal sampling based measurements with results in frequency domain.

4. The application of the method has an immediate economical effect by:

- Shortening the product qualification and its production test by lowering the time needed for tests' correlation and industrialization

- Helps the constant over time high quality of the IC production, significantly improving the quality determinative statistical indicators

- Saves rejecting of functional ICs in case of test results distribution's marginal to the test limits

- Does not engage additional computing and hardware resources

This paper presents a new developed DSP based test method for measurement in presence of timing jitter and application algorithm based on the identification of the amplitude peaks in a predefined frequency range of the sampled signal spectrum.

The method's powerful effect of suppressing the o value at very low level

independently of the jitter quantity increase is demonstrated graphically.

Experimental results of testing a lot of 150 ICs in an industrial environment are presented, using traditional DSP and the proposed method in turn, proving the high effectiveness of the last one in improving the statistics results of the tests.

#### 7. REFERENCES

- [1] Alcatel Microelectronics, C150 ASSP ATE test specification version 0.4, 2002

- [2] Alcatel Microelectronics, C150 ASSP ATE test report, October, 2002

- [3] Alan V. Oppenheim, Ronald W. Schafer, Discrete-Time Signal Processing, Prentice Hall, Englewood Cliffs, NJ, March 1989, ISBN: 013216292X

- [4] Alan V. Oppenheim et al., Signals and Systems, Prentice Hall, Englewood Cliffs, NJ, August 1997, ISBN: 0138147574

- [5] L. Shiano, M. Momenzadeh, F.-M. Zhang, Y.-J. Lee, Y. Kim, F. J. Meyer, F. Lombardi, S. Max, "Frequency Domain Measurement of Timing Jitter", 2004 IEEE IMTC

- [6] Mark and Gordon W. Roberts, An introduction to Mixed-Signal IC Test and Measurement, Oxford university press, 2001.

## CONTINUOUS WORKBENCH OF SIMULATION & DESIGN SOFTWARE TOOLS FOR EDUCATIONAL APPLICATIONS

George Angelov\*, Vassil Palankovski†, Marin Hristov\*

\* ECAD Laboratory, FETT, Technical University of Sofia, 8 Kliment Ohridski Str., 1797 Sofia, BULGARIA, phone: +359-2-965-2570, email: <a href="mailto:gva@ecad.tu-sofia.bg">gva@ecad.tu-sofia.bg</a>, <a href="mailto:mhistov@ecad.tu-sofia.bg">mhristov@ecad.tu-sofia.bg</a></a>

†Inst. für Mikroelektronik, Technische Universität Wien, Gußhausstraße 27-29, 1040 Vienna, AUSTRIA, phone: +43-1-58801-36017, email: <a href="mailto:palankovski@iue.tuwien.ac.at">palankovski@iue.tuwien.ac.at</a> (ÖFG Project MOEL+ 044, ECAD Laboratory. Technical University of Sofia. BULGARIA)

Keywords: ECAD, TCAD, SPICE, device simulation, Spectre, Minimos-NT

The state-of-the-art MOS models for simulation and device simulators are depicted. The design workflow from process via device to circuit simulation is shown. Comparison between the simulation results of the device simulator Minimos-NT and the circuit simulator Spectre are provided. On the example of a ring oscillator circuit the coherence between these simulators is demonstrated. The existence of such continuous workbench is beneficial for both educational and industrial purposes.

#### I. INTRODUCTION

Device feature sizes have been reducing over the years and now crossed below 100 nm at the mass-production level. The ultra-deep submicron and nanometer CMOS ULSI technologies imply the use of complex multilevel development paradigms where ECAD and TCAD methodologies play the major role. The challenging demand is to utilize the available technology to the utmost, while reducing design margins. A key modeling goal is to set up a consistent modeling infrastructure from process through device/circuit to systems design level. Adequate modeling and simulation are integral parts of such an infrastructure. The particular simulation tool or a combination of tools should be chosen in accordance with the design complexity, the desired accuracy, and the available human and time resources.

Traditionally, technology developers and circuit designers are largely separate entities loosely linked by a set of layout files and SPICE model parameters. In the context of shrinking ULSI technologies the need for consistent modeling flow requires a continuous workbench of simulation and design tools.

#### II. ADVANCED SPICE MODELS

Nowadays, SPICE (initially developed by University of California at Berkeley (1972)) is the most well known and a de facto standard for circuits simulation. Lots of circuit simulators are available on the market: PSPICE (OrCad, Cadence Design Systems), Spectre (Cadence Design Systems), Eldo (Mentor Graphics), HSPICE (Synopsis), Saber (Analogy), TSPICE (Tanner Research), SmartSPICE (Silvaco), Smash (Dolphin Integration), APLAC (APLAC Solutions), etc.

Initially, analytical models were built with the intent to create an understanding of transistor behavior, rather than elemental models for a circuit simulation. Later with the development of SPICE, these models were used as elemental models of the

transistors. Downscaling device sizes calls for more corrections describing the wider variety of small geometry effects. Efforts have been made to include physical effects in the device models of the major commercial simulators [1]. Accurate fitting of device data from different technologies is the most challenging task facing SPICE models.

The major industry models today are BSIM 3v3/4, MM9/11, and EKV v2.6. The most popular model, BSIM3v3 [2], is an advanced submicron model that emphasizes physical formulation, computational efficiency, and ability to accommodate a variety of technologies. EKV v2.6 is oriented towards use in low-voltage, low-power analog and mixed design and simulation with very small number of parameters. Models such as BSIM3/4 and MM9/11 (Philips) are based on threshold voltage ( $V_{Th}$ ) formulation. A disadvantage of this approach is the use of approximate expressions of  $I_{DS}$  in the weak- and strong-inversion regions, tied by a smoothing function. In result, the description of  $I_{DS}$  in the moderate inversion region is neither physical nor accurate (moderate inversion region becomes increasingly important in analog and RF design). To enlarge the physical content, model developments focus on charge sheet models based on surface potential ( $\varphi_s$ ) formulation (e.g. SP2001) [3]. These models allow an inherently single-equation and accurate calculation of  $I_{DS}$ , and could serve as basis for the next sub-100nm generation of compact models [4].

In the present work, the Cadence Spectre simulator was used to demonstrate how industrial design software compares to TCAD simulation software, particularly to Minimos-NT.

#### III. DEVICE SIMULATORS

The continuously increasing computational power of computer systems allows the use of TCAD tools on a very large scale. Several commercial device simulators (such as APSYS, ATLAS, BIPOLE3, DESSIS, G-PISCES, and MEDICI), company-developed simulators (like FIELDAY and NEMO), and university-developed simulators (such as DEVICE, FLOODS, GALENE, Minimos, nextnano3, PISCES, and PROSA) have been successfully employed for device engineering applications (for detailed review see [5]). These simulators differ considerably in dimensionality, in choice of carrier transport model (drift-diffusion, energy-transport, or Monte Carlo statistical solution of the Boltzmann transport equation), and in the capability of including electro-thermal effects. The drift-diffusion transport model is by now the most popular model used for device simulation. With down-scaling of the feature sizes, non-local effects become more pronounced and they must be accounted for by applying an energy-transport model. Quantum mechanical effects gain increased importance with the scaling of the feature size.

The device simulator PISCES developed at Stanford University incorporates modeling capabilities for various devices and includes harmonic balance for large-signal simulation. MEDICI from Synopsys, which is based on PISCES, offers hydrodynamic simulation capabilities and rigorous modeling of carrier generation

and recombination processes. DESSIS from ISE offers extensive trap modeling. The density-gradient method is used to model quantum effects.

At the quantum level a one-dimensional Schrödinger-Poisson solver. NEMO, based on non-equilibrium Green's functions is offered for sub-100 nm structures. The program SIMBA links one-dimensional Schrödinger solver with a two-dimensional Poisson solver. Quasi-two-dimensional approaches using a simplified one-dimensional current equation are demonstrated by several simulators (among others BIPOLE3 from BIPSIM). A similar approach which couples a full hydrodynamic transport model with a Schrödinger solver has been developed at the University of Leeds. A software interface between the device model and the compact Root large-signal model within the Microwave Design System has been offered by Agilent.

Several critical modeling issues are addressed in the device/circuit simulator Minimos-NT [6], which we used for preparing the following examples.

#### IV. SIMULATION RESULTS

The continuous workbench of simulation and design software includes process simulation (TSUPREM4), device/circuit simulation (Minimos-NT) and circuit simulation (Spectre). The two-dimensional device simulator is equipped with an extensive mixed-mode circuit capability including modeling of distributed devices [7]. This allows insight into the performance of devices under realistic dynamic boundary conditions imposed by a circuit. Spectre [8] is an advanced circuit simulator that uses direct methods to simulate analog and digital circuits at the differential equation level. Its basic capabilities are similar in function and application to those of SPICE.

#### IV.1 Technology and Device Simulation

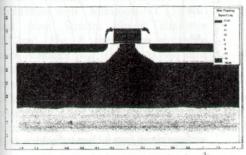

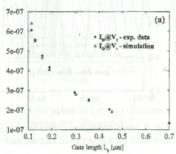

The process simulation (Fig. 1) starts from the blank wafer to the final device and reflects real device fabrication as accurately as possible. The implant profiles are calibrated to one-dimensional SIMS profiles. Process and device calibration is completed when the threshold voltage–gate length characteristic ( $V_{Th}$ – $L_g$ ) obtained by device simulation (Fig. 2) matches experimental data which indicates that the simulation includes advanced device behavior such as the reverse short channel effect and other short-channel effects [9].

Fig. 1. Net doping concentration [cm<sup>-3</sup>] in 0.35μm NMOS.

Fig. 2. Calibration of the drain current [A/μm] at threshold voltage.

**ELECTRONICS' 2004**

The physical models in Minimos-NT are well calibrated [10], especially for silicon-based devices. There are only a few technology dependent model parameters that can be used for calibration purposes. One parameter is the gate workfunction difference which depends on the interface charges at the Si/SiO<sub>2</sub> interface and the properties of the polysilicon gate. Other parameters are used to model the surface mobilities, which strongly depend on the quality of the Si/SiO interface and on the electric field distribution in the channel.

#### **IV.2 Circuit Simulation**

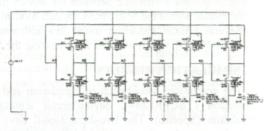

High-speed operation is a key challenge for lots of novel devices. In CMOS digital circuits with static logic, the average gate delay time of a simple inverter chain provides a useful metric for the overall circuit speed. In our example a ring oscillator circuit, consisting of five inverter chains with the output fed to the input, is used.

Fig. 3. Circuit diagram of a five stage ring oscillator.

By determining the oscillation frequency f of such a ring circuit the average gate delay time  $t_d$  of one inverter stage can be calculated using  $t_d = 1/(2nf)$  with n — number of stages (here n = 5).

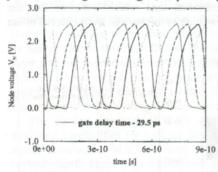

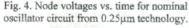

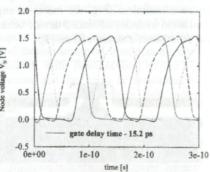

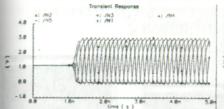

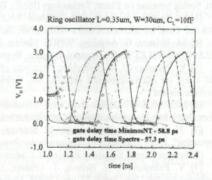

Minimos-NT can handle various sub-micron technologies. Simulation results for 0.25 µm and 0.13 µm technologies are presented in Fig. 4 and Fig. 5, respectively, which are in good agreement with experimental data [9]. Opposite to that, the Spectre model available in our Cadence Design software is calibrated for 0.35 µm technology and higher, and therefore, can be applied according to this constraint. Simulation results for devices with two different gate-widths from the 0.35 µm technology are presented in Fig. 6 and Fig. 7, respectively.

Fig. 5. Node voltages vs. time for nominal oscillator circuit from 0.13 µm technology.

Fig. 7. Node voltages vs. time for oscillator circuit from 0.35μm technology (Wg=10μm).

#### IV.3 Comparison of results

The gate length  $L_g$ , gate width  $W_g$ , and applied voltage  $V_{DD}$  for the investigated technologies are summarized in Table I, together with simulation results for the ring circuit average gate delay time obtained with both simulators.

TABLE I — Simulation results of Minimos-NT and Spectre

| Simulator      | No. | $L_g$ [um] | $W_g[um]$ | $V_{DD}[V]$ | $C_L[fF]$ | Δ[ps] | $f = 1/\Delta \text{ [GHz]}$ | t <sub>d</sub> [ps] |

|----------------|-----|------------|-----------|-------------|-----------|-------|------------------------------|---------------------|

| Minimos-<br>NT | 1   | 0.35       | 30        | 3.0         | 10        | 588   | 1.70                         | 58.8                |

|                | 2   | 0.25       | 20        | 2.5         | 5.4       | 295   | 3.39                         | 29.5                |

|                | 3   | 0.13       | 10        | 1.5         | 3.8       | 152   | 6.58                         | 15.2                |

| Spectre        | 1   | 0.6        | 30        | 3.0         | 10        | 1140  | 0.88                         | 114.0               |

|                | 2   | 0.6        | 20        | 3.0         | 10        | 1163  | 0.86                         | 116.3               |

|                | 3   | 0.6        | 10        | 3.0         | 10        | 1339  | 0.75                         | 133.9               |

|                | 4   | 0.35       | 30        | 3.0         | 10        | 573   | 1.74                         | 57.3                |

|                | 5   | 0.35       | 20        | 3.0         | 10        | 590   | 1.69                         | 59.0                |

|                | 6   | 0.35       | 10        | 3.0         | 10        | 640   | 1.56                         | 64.0                |

Since our Spectre model is calibrated for 0.35 µm technology and higher, we were able to explicitly compare these results only. As can be seen from Table I. comparable average gate delays per stage t<sub>d</sub> are obtained from device/circuit simulation with Minimost-NT (58.8ps) and from Spectre circuit simulator (57.3ps). Fig. 8 shows the simulated node voltages  $V_N$  (N=1...5) vs. time resulting from the two simulators. The established setup allows combination of ECAD and TCAD simulation tools in continuous flow, which provides a link from technology development through device development to circuit design.

Fig. 8. Comparison of node voltages simulated with Spectre and Minimos-NT.

Circuit design

# Technology simulation Device simulation Device/circuit simulation

Fig. 9. Continuous simulation workflow including TCAD and ECAD tools.

Circuit simulation

#### V. CONCLUSION

A brief overview of the state-of-the-art SPICE models and simulation tools for MOS devices was given. The coherence between the simulators Spectre (Cadence) and Minimos-NT (TU Vienna) was demonstrated by a circuit simulation example. A continuous simulation workflow was established in our laboratory (Fig. 9). We believe the new setup can be beneficial for future scientific investigations and for demonstrations with educational purposes.

#### REFERENCES

- [1] W. Liu, "MOSFET Models for SPICE Simulation, including BSIM3v3 and BSIM4", John Wiley & Sons, New York, 2001.

- [2] G. Angelov, M. Hristov, "SPICE Modeling of MOSFETs in Deep Submicron", Proc. 27th IEEE Intl. Spring Seminar on Electr. Technology (ISSE), Bankya, Bulgaria, Book 2, pp. 257-262, May 2004.

- [3] G. Angelov, T. Takov, and St. Ristic "MOSFET Models at the Edge of 100-nm Sizes", Proc. 24th Intl. Conf. on Microelectronics (MIEL), Niš, Serbia & Montenegro, Vol. 1, pp. 295-298, May 2004.

- [4] M. Hristov, G. Angelov, "SPICE Models for MOSFETs: Towards the Nanotechnology Era", "ELECTRONICS ET'2003", Sozopol, Bulgaria, Book 4, pp. 31-36, September 2003.

- [5] V. Palankovski, S. Selberherr, "Analysis of High-Speed Heterostructure Devices", Proc. 24th Intl. Conf. on Microelectronics (MIEL), Niš, Serbia & Montenegro, Vol. 1, pp. 115-122, May 2004 (keynote invited)

- [6] MINIMOS-NT Device and Circuit Simulator, Inst. für Mikroelektronik, Technische Universität Wien, 2002. http://www.iue.tuwien.ac.at/software/minimos-nt.

- [7] T. Grasser, V. Palankovski, G. Schrom, and S. Selberherr, "Hydrodynamic mixed-mode simulation", Proc. Simulation of Semiconductor Processes and Devices, Springer, 1998, pp. 247–250.

- [8] Spectre Circuit Simulator Reference, Cadence Design Systems, Product Version 5.0, June 2003.

- [9] V. Palankovski, N. Belova, T. Grasser, H. Puchner, S. Aronowitz, and S. Selberherr, "A Methodology for Deep Sub-0.25 µm CMOS Technology Prediction", *IEEE Trans. Electron Devices*, Vol. 48, No. 10, pp. 2331–2336, October 2001.

- [10] S. Selberherr, W. Hänsch, M. Seavey, and J. Slotboom, "The Evolution of the MINIMOS Mobility Model", Solid-State Electron., Vol. 33, No. 11, pp. 1425–1436, 1990.

# STUDY OF THE IMPACT OF THE TIMING JITTER ON THE STATISTICAL INDICATORS OF THE SIGNAL SAMPLING BASED MEASUREMENTS

Ivo G. Aldimirov1

<sup>1</sup>ATSA, Communications Dept., 4023 Plovdiv International Airport, Bulgaria, e-mail: aldimirov@yahoo.com;

Keywords – timing jitter, digital signal processing, statistical indicators, test results distribution.

This paper presents the results of a study focused on the impact the timing jitter has on the statistical indicators of the signal sampling based tests.

#### 1. INTRODUCTION

The statistical indicators of the quality tests in production have crucial importance for the overall quality and cost of the new produced integrated circuits (IC) [8, 9]. The process of qualification of the new developed IC goes through the detailed investigation of the statistical indicators - Cp,  $Cp\kappa$  and standard deviation –  $\sigma$  of all tests in the product specification [6, 8, 9]. Lower values of Cp and  $Cp\kappa$  might lead to prolonged industrialization process of the IC, quality loss and cost increase as well as longer time-to-market period.

This paper presents the results of a study focused on the impact the timing jitter has on the statistical indicators of the digital signal processing (DSP) based tests. It is presented the mathematical model of the process of signal sampling in the presence of timing jitter. It is given the analytical equation describing the relation between the standard deviation and the timing jitter quantity.

### 2. STATISTICS PROBLEMS OF THE DSP BASED MEASUREMENTS IN THE PRESENCE OF TIMING JITTER

In the base of the DSP based test methods is the amplitude measurement of a known spectrum component of interest defined in the test program - spectral bin, frequency of interest. The presence of timing jitter in the signal sampling process has severe impact on the measurement accuracy and repeatability. The effect of jitter can be associated with a random timing variable denoted as tj, and added to the period T of the sampled signal. The result of the amplitude measurement of frequency bin corresponding to the frequency of interest will bring information not only for the spectral bin of interest but also for the neighboring ones in the signal spectrum. This is easily seen in fig. 1, where the overlapped results in frequency domain of the several times repeated measurement of a sampled signal with timing jitter is presented.