## ANNUAL JOURNAL

**OF**

## **ELECTRONICS**

#### ANNUAL JOURNAL OF ELECTRONICS

#### EDITOR'S BOARD

**President:**

Prof. Dr. Racho Ivanov

**Vice President:**

Prof. Dr. Marin Hristov

Members:

Prof. Dr. Stefan Ovcharov

Prof. Dr. Georgy Mihov

Assoc. Prof. Dr. Petar Yakimov

The Journal is issued by the FACULTY OF ELECTRONIC ENGINEERING AND TECHNOLOGIES, TECHNICAL UNIVERSITY of SOFIA, BULGARIA.

The Journal includes the selected papers from the International Scientific Conference Electronics '12, held on 19-21 September 2012 in Sozopol, Bulgaria.

<sup>© 2012</sup> Faculty of Electronic Engineering and Technologies, Technical University of Sofia, Bulgaria.

## **CONTENTS**

### BOOK 2

| Vavilov Vl., Modeling Thermal NDT Problems                                 | 1   |

|----------------------------------------------------------------------------|-----|

| Vainshtein S., G. Duan and J. Kostamovaara, Avalanche Bipolar Transistor:  | 9   |

| 60 Years Old, but Modern Device with New Advances                          |     |

| Duan G., S. Vainshtein and J. Kostamovaara, Effect of Spatial Triggering   | 15  |

| Inhomogeneity on 3-D Transient in a High-current Avalanche                 | 10  |

| Transistor                                                                 |     |

| Yordanov R. S., J. I. Ivanov, Automated Design System for Gate Array-based | 19  |

| Bipolar Integrated Circuits                                                | 1)  |

| Nikolov D. N., D. Pissoort, E. D. Manolov, M. H. Hristov and R. De         | 23  |

| Craemer, Development of RF Energy Scavenging System in the Area            | 23  |

| of KHBO - Ostend                                                           |     |

| Gaydazhiev D. G., I. St. Uzunov and G. O. Georgiev, Opportunities for      | 27  |

| Passband Bandwidth Extension in FBAR Ladder Filters                        | 21  |

| Gieva E. E., Behavioral Modeling of a Circuit Functionally Analogous to    | 31  |

| Hydrogen Bonding Network with Water Molecules                              | 31  |

|                                                                            | 35  |

| Rusev R. P., G. V. Angelov, E. E. Gieva, B. P. Atanasov and M. H. Hristov, | 33  |

| Microelectronic Aspects of Hydrogen Bond Characteristics in Active         |     |

| Site of β-lactamase during the Acylenzyme Reaction                         | 20  |

| Spasova M. L., G. V.Angelov and M. H. Hristov, Simulation of 1T DRAM       | 39  |

| Memory Cell with Verilog-A Model of CNTFET in Cadence                      | 4.0 |

| Raykov K. T. and V. H. Videkov, Problems in Wire Bonding Process           | 43  |

| Videkov V. H. and R. I. Radonov, New Considerations for the Design of IC   | 46  |

| Bond Pads Using CAD Systems                                                |     |

| Bankova A. G. and V. H. Videkov, Measuring the Stability of Nanomaterials  | 49  |

| Toteva I. Pl. and A. Vl. Andonova, Modeling Snapback Characteristic with   | 51  |

| SCR-based Device Using PSpice                                              |     |

| Andonova A. Vl., Al. P. Radev and K. V. Stankulov, Accelerated Aging for   | 55  |

| LEDs                                                                       |     |

| Andonova A. Vl., Formation of Thermal Compact Model                        | 59  |

| Delibozov N. G., R. I. Radonov and M. H. Hristov, Evolution of Integrated  | 63  |

| MEMS Design Methodology                                                    |     |

| Aleksandrova M. P. and A. Ozturk, Capacitive MEMS Compression Sensor       | 66  |

| for Touchscreen Display Applications                                       |     |

| Bouras M. and A. Hocini, Study of Birefringence in Hybrid Magneto-Optical  | 70  |

| Thin Film on Ion-Exchanged Glass Waveguide                                 |     |

| Vavilov Vl., D. Nesteruk and Vl. Khorev, Ultrasonic and Inductive IR       | 74  |

| Thermographic Procedures as Newly-Emerged Techniques in Thermal            |     |

| NDT                                                                        |     |

| Hotra Z. Y. and L. Y. Voznyak, Development of Green OLED Structures        | 78  |

| Based on Organic Semiconductor Alq3                                        |     |

| Spasov G. S., Auger Electron Spectroscopy for Investigation in                          | 80   |

|-----------------------------------------------------------------------------------------|------|

| Microelectronics                                                                        |      |

| Spasov G. S., Auger Electron Spectroscopy for Investigation of Aluminium Nitride Layers | 84   |

| Kolev G. D., Investigation of Piezoelectric Effect in Thin Layers, for                  | 88   |

| Application in Harvesting Devices and MEMS Sensors                                      |      |

| Brusev T. S., DC – DC Converter Integrated on CMOS 0.35 μm Technology                   | 91   |

| Hotra Z. Y., Z. M. Mykytyuk, A.V. Fechan, O. Y. Sushynskyy and O. V.                    | 95   |

| Chaban, Magnetically Controlled Liquid Crystalline Structures for                       |      |

| Fiber-Optic Link                                                                        |      |

| Hotra Z. Y., Z. M. Mykytyuk, O. Y. Sushynskyy, O. Y. Shymchyshyn and V.                 | 99   |

| St. Petryshak, Sensitive Element of Carbon Monoxide Sensor Based                        |      |

| on Liquid Crystals Doped by Nanosized Fe                                                |      |

| Hotra Z. Y., D. Y. Volynyuk and N. V. Kostiv, Investigation of Solar Cell               | 103  |

| Based on ITO/CuI/SubPc/C60/Al Heterostructure                                           |      |

| Pashinski Ch. O., R. D. Kakanakov, L. P. Kolaklieva, T. M.Cholakova and C.              | 105  |

| P. Bahchedjiev, Even Distribution of the Thickness of Coatings                          |      |

| Produced by Vacuum Arc Deposition on Large Parts                                        |      |

| Shindov P. C., V. Smatko, T. G. Anastasova and V. St. Serbezov, Nah                     | 109  |

| Modification of CdSSe Layers Properties by Fast CW CO2 Laser                            |      |

| Annealing                                                                               |      |

| Denishev K. H., G. B. Kadijski, G. D. Kolev and D. G. Gaydazhiev, Design                | 113  |

| and Investigation of RF MEMS Switch with Piezoelectric Actuation                        |      |

| Shoikova E. D., and M. Y. Krumova, Innovative Learning Scenario Design                  | 117  |

| Yordanov R. St., R. Sl. Mitev and G. Dimitrov, Interactive Education in                 | 121  |

| Microelectronics                                                                        |      |

| Goranova M. E. and L. J. Stoyanova, Effective Query Implementation of                   | 125  |

| Scientific Data Based on LINQ to XML                                                    |      |

| Goranova M. E., L. Y. Stoyanova and P. B. Peev, A Web Service for                       | 129  |

| Statistics Generation in Educational Process                                            |      |

| Stoimenov E. Ch. and I. M. Pandiev, An Educational Electronic Prototype                 | 133  |

| System for Phase-Locked Loop - Based Circuits                                           |      |

| Mitov K. M. and I. A. Bozhilov, Preparing Students for International Robotics           | 137  |

| Competitions                                                                            |      |

| Tchoumatchenko V. Pl., T. K. Vasileva and M. E. Goranova, A Lightweight                 | 141  |

| Learning Content Management System                                                      |      |

| Todorova V. D. and Sv. S. Kamenov, Program Module for Calculating                       | 145  |

| Constructional Dimensions of Passive Microelectronic Components                         |      |

| Cordemans P., J. Boydens and E. Steegmans, Deterministic State Space                    | 149  |

| Exploration for Concurrent Embedded Software                                            | 1.50 |

| Catteeuw W., P. Cordemans and J. Boydens, Integration of a CANopen                      | 153  |

| Protocol Stack in an Embedded Application Employing the                                 |      |

| CANFestival Stack                                                                       | 1.55 |

| Vincke R., S. V. Landschoot, E. Steegmans and J. Boydens, Refactoring                   | 157  |

| Sequential Embedded Software for Concurrent Execution Using                             |      |

| Design Patterns                                                                         |      |

| Coudyzer G., St. De Lausnay, N. Steven, JP.Goemaere and L. De Strycker, Performance Analysis and Optimization of the Combined-Contour | 161 |

|---------------------------------------------------------------------------------------------------------------------------------------|-----|

| Labeling Algorithm for Real-Time Applications                                                                                         |     |

| Naydenov T. B. and P. G. Manoilov, FPGA Implementation of XR Router for                                                               | 165 |

| Alpha Omega Highway SAN                                                                                                               |     |

| Kireva T. T., FPGA Implementation of System on a Chip, Using 32-bit RISC                                                              | 169 |

| Core                                                                                                                                  |     |

| Badarov D. H. and G. Sl. Mihov, Universal Digital Counter Based on Xilinx                                                             | 173 |

| FPGA                                                                                                                                  |     |

| Spirov R. P., P. N. Tzanov and N. St. Grancharova, Adaptive FPGA System of                                                            | 177 |

| Recognition Dynamic Objects                                                                                                           |     |

| Bogdanov L. V. and R. M. Ivanov, Approaches for Reducing the Power                                                                    | 181 |

| Consumption in Embedded Systems                                                                                                       |     |

| Brusev T. S. and B. M. Nikolova, Reliability and Power Supply Voltages of                                                             | 185 |

| Embedded System Platforms                                                                                                             |     |

| Dilov K. D. and E. N. Dimitrov, Software Integrated Environment for Real-                                                             | 189 |

| Time System Design and Analysis                                                                                                       |     |

| Spasov G. V., Open Source Hardware in Education on Embedded Systems for                                                               | 193 |

| Non-EE Students                                                                                                                       |     |

| Petrov B. B., Application of the Programmable Logic Devices for                                                                       | 197 |

| Implementation of In-circuit Tester for Microprocessor System                                                                         |     |

| Chayleva I. K., M. A. Botev, V. Pl. Dobreva and B. B. Petrov, Methods and                                                             | 201 |

| Techniques for Real-Time Audio Data Streaming to and from High                                                                        |     |

| Capacity Local DSP SDRAM Memory                                                                                                       |     |

|                                                                                                                                       |     |

# DC – DC Converter Integrated on CMOS 0.35 µm Technology

#### Tihomir Sashev Brusev

Abstract – DC – DC converter is designed and integrated on CMOS 0.35  $\mu m$  technology. Investigations results of efficiency and power losses are presented. Different control techniques of monolithic buck converter system are developed.

Keywords - dc - dc converter, CMOS technology, efficiency, power losses

#### I. INTRODUCTION

In the modern electronic equipments different power supply voltages for the building blocks are needed. DC -DC converters with high efficiency are required to be designed [1]. A way to decreasing the size, weight and consequently the price of these devices is miniaturizations. The integration is the present and future of the electronic technique for many applications. Fully monolithic dc - dc converter could reduce the volume of the devices. The tendency in microelectronics nowadays is to continuously scale down the standard CMOS process technology, which leads to decreased breakdown voltages. In battery-powered electronic devices, however, the battery voltage remain relatively constant and it should be converted to the desired voltage levels with minimum energy loss. The requirement to increase the battery life and the system run-time of these devices becomes stringent. To reduce the power dissipations is necessary subsystems to operate at its optimum supply voltages.

A high switching frequency is the key design parameter, which help to make monolithic integration of active and passive devices. At this high switching frequency, the energy dissipated in power MOS transistors dominates the total losses in dc-dc converter. To receive the best possible efficiency we need to operate exactly at the frequency, where the inductor of low-pass filter has maximum quality factor Q. In CMOS technology, passive components and especially integrated inductor are very lossy. The passive components are for energy storage and output filtering.

The custom designed monolithic voltage converters for individual loads have high efficiency and their volumes are small. The standard PWM control, which is constant frequency method, is widely used to maintain a fixed voltage to output of the converter. When the converter operates with high load, the circuit work in the basic mode and high efficiency could be achieved. In most of the portable electronic devices, a light-load operation or standby mode is a key to achieve longer battery life, and at this mode the system should also indicate high efficiency.

This paper presents dc - dc monolithic buck converter designed on 0.35- $\mu$ m CMOS technology. Section II is divided into three parts. In Section II A efficiency

T. Brusev is with the Department of Technology and Management of Communication Systems" Faculty of Telecommunications, Technical University of Sofia, Kl. Ohridski 8, 1797 Sofia, Bulgaria, E-mail: brusev@ecad.tu-sofia.bg.

investigations results as function of different circuit's parameters are given. Power losses evaluations are presented Section II *B.* In Section II *C* developed PWM and PFM controls of the designed buck converter are described.

#### II. INVESTIGATIONS

#### A. Efficiency investigations

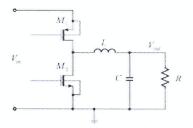

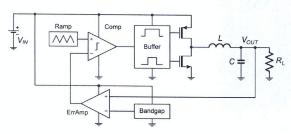

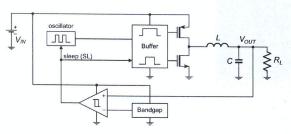

Figure 1 shows the circuit of a buck converter implemented on standard CMOS 0.35-μm technology. The NMOS and PMOS transistors, which are forming the power stage, are synchronously controlled in a way that when one of the transistors is switched-on the other is switched-off. In the following, the efficiency performance of the power stage is evaluated assuming ideal drivers with the goal to select an appropriate switching frequency and filtering components.

Figure 1. Synchronous buck converter schematic.

One of the most important parameters in the dc-converters is efficiency:

$$\eta = \frac{P_{OUT}}{P_{IN}} \tag{1}$$

where  $P_{OUT}$  is the average output power,  $P_{IN}$  is the average input power of the converter. The losses in power stage of buck converter are much higher compare to the energy dissipation in the feedback control system [2]. They dominate and determine the efficiency of the system.

The power losses in the filter inductor can seriously decrease the overall efficiency of the converter's system. Integration of whole dc - dc converter together with passive filter's inductor and capacitor is possible at high switching frequency  $f_s$ . On the other hand this leads to increasing of power losses in CMOS integrated circuits. The disadvantages of monolithic inductors are that they are usually with low inductance, occupied large silicon area and have low quality factor Q.

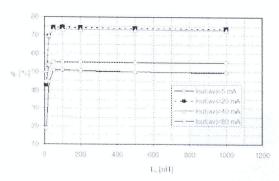

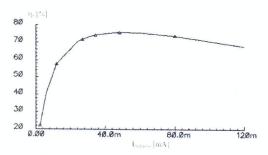

The influence of the filter's inductor value L over the efficiency of the synchronous buck converter is investigated. The received results are achieved by simulations using Cadence design tools. In Figure 2 is presented efficiency  $\eta$  of the evaluated circuit as a function L at different load currents.

Figure 2. Efficiency of the designed monolithic back converter as a function of filter inductor L at different load currents  $I_{out(av)}$ .

As can be seen from the picture at small inductor's values  $\eta$  of the investigated circuit is decreasing dramatically. The best efficiency results are achieved at load current equal to 20 mA, because for that current are optimized the sizes of N and P channel power MOS transistors.

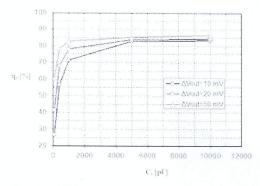

The price and volume of electronic equipments is one of the major factors in their design. There are restrictions on the value and the chip area, which can occupy integrated filter capacitor in monolithic buck converter [3]. The effect of the maximum allowable output voltage ripple over efficiency performance of the converter is investigated. The influence of the capacitor value over the system efficiency is evaluated. The output voltage ripple is kept constant at three different levels respectively 10~mV, 20~mV u 50~mV. The investigations are made are average load current equal to  $I_{out(av)} 20~\text{mA}$ .

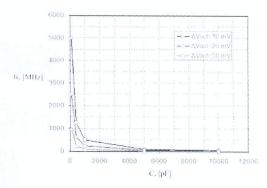

In Figure 3 are presented received simulations results of the buck converter's efficiency  $\eta$  as function of filter capacitor C.

Figure 3. Efficiency of the designed monolithic buck converter as a function of filter capacitor C at different maximum allowable output voltage ripple  $\Delta V_{out}$ .

In Figure 4 is presented relationship between switching frequency  $f_s$  and output filter capacitor C of the synchronous buck converter, when output voltage ripple is kept constant. As can be seen from the picture, higher  $\Delta V_{out}$  leads to decreasing of  $f_s$  in order to maintain a constant value of output voltage and inductor current ripple  $\Delta I_L$  at fixed value of. At lower switching frequency losses in the power MOS transistors goes down. Thereby reducing the requirements to output voltage ripple  $\Delta V_{out}$  is increasing the efficiency of monolithic buck converter at fixed filter capacitor C.

Figure 4. Switching frequency  $f_s$  of the designed monolithic buck converter as a function of filter capacitor C at different maximum allowable output voltage ripple  $\Delta V_{out}$ .

Decreasing the switching frequency  $f_s$  is increased the reliability of the whole integrated buck dc-dc converter system, because the design of PWM control technique became simple.

#### B. Power losses investigations

At high switching frequencies the losses in the transistors are inadmissibly large and the efficiency of the converter decreases:

$$\eta = \frac{P_{OUT}}{P_{IN}} = \frac{P_{OUT}}{P_{OUT} + P_{LOSS}} \tag{2}$$

where  $P_{LOSS}$  are all power losses occurring in the power transistors, as well as in the controlling stages. To obtain high converter efficiency, all conversion losses should be kept to a minimum. The conducting losses in the transistors are proportional to the switching frequency  $f_s$  and the rmsvalue of the current flowing through the device 0. This relationship is repeated bellow:

$$P_{MOS} = k_1 i_{rms}^2 + k_2 f_s \tag{3}$$

where kI and k2 is are technology dependent coefficient, which are taking into account the size of the power MOS, as well as the resistive and the capacitive losses associated with the MOS structure. Small inductor ripple current will result in smaller rms-value of the current through the MOS structure, and it will respectively lead to better efficiency.

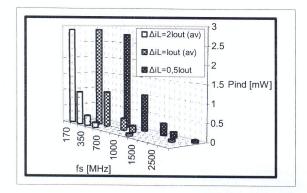

Power losses in filter inductor of designed monolithic dc-dc converter are evaluated.

Figure 5. Power losses in the filter inductor of buck converter of fs and  $\Delta I_L$ , for Iout (av)=20 mA.

In Figure 5 are presented received simulations results. Power losses in the filter inductor are investigated as a function of switching frequency  $f_s$  and inductor current ripple  $\Delta I_L$  at  $I_{out(av)}$ =20 mA. The received results show that by increasing of switching frequency  $f_s$  of the circuit power dissipations in the filter inductor decreased. By increasing of the  $\Delta I_L$  requirements for the inductor's value decreased for fixed switching frequency  $f_s$ . This reduces the parasitic impedance of the filter inductor and the related power loss. A higher value of the  $\Delta I_L$  leads to the increasing of rms current through the inductor which causes to the bigger conduction losses in the inductor.

#### C. PWM and PFM controls

Figure 6. PWM block diagram

The block diagram of the switching-mode DC-DC buck converter system using standard PWM control loop is shown in Figure 6. The system consists of bandgap reference, error amplifier, ramp generator, comparator, buffer and power buck stage. The power losses in the controlling stages are minimized in order to improve the overall converter efficiency  $\eta$ . The nominal supply voltage of the converter is 3.6 V and steps-down to 1.2. The system operates at switching frequency  $f_s$  of 150 MHz.

The bandgap voltage reference provides a stable voltage for the whole converter system that is independent from the power supply, load current, and temperature variations. This stage consumes only 0.27 mA, which helps to improve  $\eta$ .

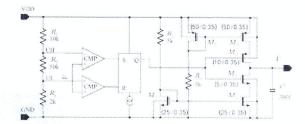

The error amplifier determines the control voltage, which amplifies the difference between the output voltage  $V_{out}$  and the reference voltage  $V_{ref}$ . The ramp generator is a part of the regulation system, which performs the Pulse-Width Modulation (PWM) control. This stage determines the switching frequency  $f_s$  of the buck converter. In Figure 7 is shown designed circuit of ramp generator.

Figure 7. Ramp Generator.

This circuit helps to whole designed buck converter system to react when input voltage is changed. When  $V_{in}$  jumps the threshold voltages of two comparators, which are included in the ramp generator, are changed. The reason is simple resistive divider consist of  $R_I$ ,  $R_3$  and  $R_5$ . Therefore duty cycle of the control circuit is changed eliminating delay of the output reaction of the buck dc-dc converter system.

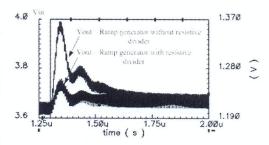

In Figure 8 are presented reactions of synchronous dc-dc buck converter system respectively with ramp generator including resistive divider and with ramp generator without resistive divider, when input voltage  $V_{in}$  jumps.

Figure 8. Reactions of synchronous dc-dc buck converter system respectively with ramp generator including resistive divider and with ramp generator without resistive divider, when input voltage V<sub>m</sub> jumps.

The control pulses for the power transistors are generated by comparing the sawtooth signal generated by the ramp generator and the control signal from the error amplifier. The comparator generates rectangular pulses whose duty-cycle is a function of the output voltage, and the PWM control loop regulates the output to the desired value.

The buffer stage delivers the controlling pulses for the power transistors. The short-circuit losses are prevented by providing a short gap time during which the NMOS and the PMOS transistors are both switched-off 0. Thus, power losses generated due to this phenomenon are avoided.

In Figure 9 is presented efficiency of the designed buck dc-dc converter as function of average load current  $I_{out(av)}$ .

Figure 9. Efficiency of the designed buck de-de converter as function of average load current  $I_{out \, tory}$ .

As can be seen from the picture efficiency of the buck dc-dc converter system is decreasing dramatically at lightload. PFM control technique is developed to improve the performance of the designed system at these conditions.

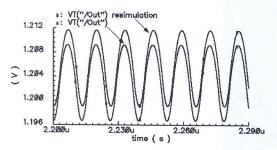

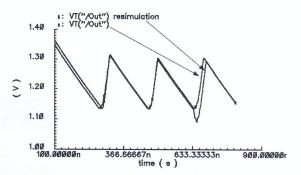

In Figure 10 are illustrated output voltages  $V_{out}$  of the converter respectively before and after layout design of the integrated circuit, when PWM control technique is used.

Figure 10. Output voltage V<sub>out</sub> respectively before and after layout design when PWM control technique is used.

Figure 11. PFM block diagram

The block diagram of the converter utilizing a PFM control technique is shown in Figure 11. Here, a generator with a fixed duty-cycle (50%) is used to drive the power transistors. The voltage regulation is achieved by turning on and off the control loop. When the output voltage exceeds a predefined value, the comparator generates a control signal, which puts the whole system in sleep mode. In sleep mode, the filtering capacitor C delivers power to load, while all active blocks are disabled, except the comparator and the bandgap. When the output voltage goes below certain value, the comparator wakes up the system

and the normal operation is restored. This technique allows minimization of the static control block consumption in light-load conditions, thus the overall efficiency is improved.

In Figure 12 are illustrated output voltages  $V_{out}$  of the converter respectively before and after layout design of the integrated circuit, when PFM control technique is used.

Figure 12. Output voltage  $V_{out}$  respectively before and after layout design when PFM control technique is used.

#### III. CONCLUSION

In this paper dc – dc buck converter integrated on CMOS  $0.35~\mu m$  technology is presented. Efficiency of whole system is investigated as a function of different circuit parameters. Power losses in the power stage are evaluated. PWM and PFM control techniques are developed. Resimulation results after layout design of the integrated circuit show good overlapping.

#### **ACKNOWLEDGMENTS**

The research described in this paper was carried out within the framework of UNIK Project DUNK – 01/03 – 12.2009

#### REFERENCES

[1] Enslin J. H. R, M. S. Wolf, D. B. Snyman, and W. Swiegers, *Integrated Photovoltaic Maximum Power Point Tracking Converter*, IEEE Trans on Industrial Electronics, Vol. 44, NO. 6, , pp. 769-773, December 1997.

[2] Kurson V., S. G. Narenda, V. K. De, and E. G. Friedman, Monolithic DC-DC Converter Analysis and MOSFET Gate Voltage Optimization, Proceedings of the IEEE International Symposium on Quality Electronic Design, pp. 279-284, March 2003.

[3] Jaeseo Lee, G. Hatcher, Evaluation of Fully-Integrated Switching Regulators for CMOS Process Technologies, IEEE Trans. on Very Large Scale Integration(VLSI) Systems, Vol. 15, NO.9, pp. 1017-1027, 2007.

[4] V. Kursun, Analysis of Buck Converter for On-Chip Integration With a Dual Supply Voltage Microprocessor, IEEE Trans. on VLSI Systems, Vol. 11, No.3, pp. 514-522, 2003.

[5] C. F. Lee and P. Mok, A monolithic Current-Mode CMOS DC-DC Converter With On-Chip Current Sensing Technique, IEEE J. Solid-State Circuits, Vol. 39, No.1, pp. 3-14, 2004.