## ANNUAL JOURNAL

**OF**

# **ELECTRONICS**

Micro- and nanoelectronics

Technologies in Electronics

Quality and Reliability in Electronics

Education in Electronics

Power Electronics

Technical University of Sofia

Faculty of Electronic Engineering and Technologies

## ANNUAL JOURNAL OF ELECTRONICS

### **EDITOR'S BOARD**

**President:**

Prof. PhD Racho Ivanov

**Vice President:**

Prof. PhD Marin Hristov

**Members:**

Prof. PhD Stefan Ovcharov

Prof. PhD Georgy Mihov

Prof. PhD. Petar Yakimov

Prof. PhD. Mityo Mitev

The Journal is issued by the FACULTY OF ELECTRONIC ENGINEERING AND TECHNOLOGIES, TECHNICAL UNIVERSITY of SOFIA, BULGARIA.

The Journal includes the selected papers from the International Scientific and Applied Science Conference ELECTRONICS'10, held on 22 - 24 September 2010 in Sozopol, Bulgaria.

The contributions are reproduced directly from the originals presented to the Organizing Committee

© 2010 Faculty of Electronic Engineering and Technologies, Technical University of Sofia, Bulgaria.

## CONTENTS

## BOOK 1

| Vainshtein, S., V. Yuferev, J. Kostamovaara, V. Palankovski, Collapsing Field Domains     |         |

|-------------------------------------------------------------------------------------------|---------|

| in Avalanche Gaas Transistor: Peculiar Phenomenon and Prospective                         |         |

| Applications                                                                              | bl p12  |

| Vitanov, S., V. Palankovski, Electron Mobility Models for III-Nitrides                    | bl p18  |

| Duan, G., S. N. Vainshtein, J. T. Kostamovaara, Physical Interpretation of "Soft" Surface |         |

| Breakdown Typical of GaAs Avalanche Transistors                                           | b1 p22  |

| Duan, G., S. N. Vainshtein, J. T. Kostamovaara, Self-Organizing of Avalanche Transistor   |         |

| Operating Area in Accordance with Parameters of External Circuit                          | b1 p26  |

| Machan, L., P. Steffan, Accumulation Mode MOS Structure Usage in the Analog Design        | b1 p30  |

| Videkov, V. H., R. I. Radonov, Die Packaging Methods and Their Relation to the Layout     |         |

| of Integrated Circuits                                                                    | b1 p33  |

| Radonov, R. I., Considerations for the Design of Bond Pads in Integrated Circuits Using   |         |

| CADENCE                                                                                   | b1 p36  |

| Brusev, T. S., M. H. Hristov, B. M. Nikolova. Investigations of Power Losses in Off-      |         |

| Chip and On-Chip Inductors                                                                | b1 p38  |

| Gieva, E. E., R. P. Rusev, G. V. Angelov, M. H. Hristov, T. B. Takov, Microelectronic     |         |

| Differential Amplifier Functionally Analogous to Hydrogen Bonding Network                 | b1 p42  |

| Rusev, R. P., G. V. Angelov, I. D. Panayotov, M. H. Hristov, T. B. Takov, Matlab and      |         |

| Verilog-A Models of Solar Cells                                                           | b1 p46  |

| Nikolov, D. N., F. T. Koparanov, M. H. Tsanov, E. D. Manolov, M. H. Hristov, Energy       |         |

| Harvesting Transducers: An Overview                                                       | b1 p50  |

| Nikolov, D. N., E. D. Manolov, M. H. Hristov, M. H. Tsanov, F. T. Koparanov,              |         |

| Architecture of Energy Harvesting Devices                                                 | b1 p54  |

| Bobeva, S. D., M. H. Hristov, K. H. Denishev, Overview of Automotive MEMS Sensors         | bl p 58 |

| Yordanov, R. S., M. H. Hristov, H. L. Yatanski, Interactive Learning Relative to          |         |

| MCM Design                                                                                | b1 p62  |

| Velev, R. Grigorov, S. I. Ivanov, Methods for Measuring of Small Capacitance              | b1 p65  |

| Karachomakov, A. N., Power-On-Reset Schematic with Low-Voltage Flag Generation            |         |

| Circuitry with Build—in Initial State                                                     | b1 p69  |

| Arnaudov, R. G., Impact of Via Shielding on Parasitic Coupling and Cavity-Resonance       |         |

| Modes in Multilayer Packages and MCMs                                                     | b1 p72  |

| Dvořák, P., M. Macalík, M. Kunovjánek, V. Musílek, O. Čech, Liquid Electrolytes for       |         |

| Electrochemical Energy Sources                                                            | b1 p79  |

| Kunovjánek, M., J. Hýbl, New Types of Membranes for Water Electrolyser                    | b1 p82  |

| Vesely, A., J. Vanek, J. Stencel, J. Dolensky, System for Automatic Recognizing           |         |

| Defects in Solar Cells                                                                    | b1 p84  |

| Prasek, J., J. Chomoucka, J. Policky, New Approach to Polymer Screen-printed              |         |

| Electrodes Enhancement                                                                    | b1 p88  |

| Adamek, M., M. Reznicek, J. Prasek, The Thermal Processes in Milk Production              |         |

| Monitoring by the Simple Thermodynamic Sensor                                             | b1 p91  |

| Huran, J., P. H. Shindov, V. Smatko, A. Valovic, A. P. Kobzev, Electrical and Optical     |         |

| Characterization of PECVD Silicon Carbon Nitride Thin Films                               | b1 p94  |

| Stratev, A. B., Component Recognition Algorithms in Automated Assembly                    | b1 p97  |

| Aleksandrova, M. P., M. M. Rassovska, K. A. Gesheva, D. V. Petkov, V. P. Petkov,          |         |

| Preparation of Electron Injecting Layers for Polyfluorenevinylene-Based                   | 11 100  |

| Electroluminescent Structures                                                             | b1 n100 |

| Mladenova, D. L., R. H. Kazacov, D. B.a Karashanova, V Milenkov, T. S. Dobreva, D.   |         |

|--------------------------------------------------------------------------------------|---------|

| S. Budurova, V. A. Sinigersky, I. T. Zhivkov, Optimization of Thin                   |         |

| Polyvinylcarbazole Spin Coated Films Applicable in Organic Based Devices             | bl p104 |

| Denishev, K. H., I. F. Ivanov, MEMS Generators for Microdroplets                     | b1 p108 |

| Kolev, G. D., K. H. Denishev, S. D. Bobeva, Design and Analyzing of Silicon          | =       |

| Diaphragm for MEMS Pressure Sensors                                                  | b1 p112 |

| Boyadzhiev, S. I., M. M. Minkova - Rassovska, Preparation and Characterization of    | •       |

| Reactive Sputtered ITO Thin Films                                                    | b1 p116 |

| Vervenne, I., J. Catrysse, G. Deconinck, Comparison of Reliability Prediction        | •       |

| Analysis and HALT of an Electronic System                                            | b1 p120 |

| Milanov, P. M., N. G. Kenarov, FPGA Platform for Support Digital and Mixed-signal    |         |

| Design Development                                                                   | b1 p124 |

| Farkov, G. A., M. Camminadi, Approaches for Automated PCB Measurements               | b1 p127 |

| Videkov, V. H., G. A. Farkov, B. R. Tzaneva, I. A. Vrublevski, Investigation of      | 1       |

| Nanostructured Objects Using Cross-section Techniques                                | bl p130 |

| Andonova, A. V, S. V. Todorov, Buried Objects Detection by Thermography              | b1 p133 |

| Andonova, A. V., A. P. Radev, Degradation Analysis for Light Emitting Diodes         | b1 p137 |

| Peuteman, J., J. Baert, R. De Craemer, P. Knapo, Implementing DSP Course Modules     | or pro, |

| with Multimedia Oriented Projects                                                    | bl p141 |

| Shoikova, E. D., M. J. Krumova, O*NET and Competency Based Education                 | bl p145 |

| Shoikova, E. D., M. J. Krumova, Overview of the Occupational Information Network     | bl p152 |

| Ivanova, M. S., J. Alam, Wave for Personal Learning Network Forming and for          | 0. p.c. |

| Collaborative Knowledge Transfer                                                     | bl p157 |

| Vasileva, T. K., V. P. Tchoumatchenko, Knowledge Practices Laboratory                | bl p161 |

| Kostadinov, A. N., Using Logisim and MiSim DE Software Tools in the Digital          | or pror |

| Logic and Microprocessor Design Subject                                              | bl p165 |

| Spasova, N. V., Implementing an Electronic System for Assessment in                  | 01 p103 |

| Engineering Education                                                                | bl p169 |

| Peuteman, J., P. Devlies, J. Knockaert, G. Vandecasteele, T. Verbeerst, I. Vervenne, | or prox |

| Laboratory Setup for Teaching Reflection Phenomena between a PWM Inverter            |         |

| and an Induction Motor                                                               | bl p172 |

| Yankov, P. V, V. C. Valchev, Power/Frequency Characteristics of Passive Controlled   | 01 p1/2 |

| Wind Turbines with Additional Reactive Components in the Circuitry                   | bl p176 |

| Valchev, V. C., P. V. Yankov, Improvement on Passive Controlled Wind Turbines        | 01 91/0 |

| Schematics and Obtaining Power/Frequency Curves                                      | bl p180 |

| Gigov, G. H., G. T. Kanov, E. I. Popov, Steady – State and Transient Processes in a  | 01 p100 |

| Current–Fed Inverter Supplied from a Buck DC – DC converter                          | b1 p184 |

| Hinov, N. L., D. D. Arnaudov, N. P. Gradinarov, G. V. Kraev, Comparative Analysis    | or pro  |

| of Circuits with Limitation of the Voltage over Commutating Inductance in            |         |

| Force-Commutating Mode of the Devices                                                | bl p188 |

| Hinov, N. L., D. D. Arnaudov, G. V. Kraev, S. V. Georgiev, Study of Photovoltaic     | or proo |

| Systems for Supplying DC Loads                                                       | bl p192 |

| Vuchev, A. S., N. D. Bankov, G. P. Terziyski, Analysis of LCC Resonant DC-DC         | 01 p132 |

| Converter with Capacitive Output Filter                                              | bl p196 |

| Vuchev, A. S., N. D. Bankov, G. P. Terziyski, Load Characteristics of LCC            | 01 p130 |

| Resonant DC-DC Converter with Capacitive Output Filter                               | b1 p200 |

| Mareva, D. J., D. D. Yudov, E. M. Marev, Inverter for Induction Heating of Fluids    | b1 p204 |

| Popov, E. I., L. I. Pindeva, S. T. Tsolov, Three – Dimensional Generalized           | 01 p201 |

| Characteristics of Autonomous Serial R L C Inverters without Free – Wheeling         |         |

| Diodes                                                                               | h1 n208 |

# Investigations of Power Losses in Off-Chip and On-Chip Inductors

Tihomir Sashev Brusev, Marin Hristov Hristov and Boyanka Marinova Nikolova

Abstract – This paper includes investigations of power losses in off-chip and on-chip filter inductors in monolithic dc-dc converter designed on CMOS 0.35 µm technology. Chip coils of the company Murata are used for off-chip inductors. For the extraction of the model's parameters of integrated inductors of CMOS 0.35 µm process is used one of the Cadence tools named "Virtuoso Passive Component Designer". Comparison between power losses in off-chip and on-chip inductors is made.

Keywords - power losses, off-chip and on-chip inductors, dc-dc converters.

#### I. INTRODUCTION

The fully monolithic dc-dc converters can reduce the cost and size of the battery powered portable electronic devices. One of the most important parameters in the dc-converters is efficiency:

$$\eta = \frac{P_{OUT}}{P_{IN}} \tag{1}$$

where  $P_{OUT}$  is the average output power,  $P_{IN}$  is the average input power of the converter. The losses in power stage of buck converter are much higher compare to the energy dissipation in the feedback control system [1]. They dominate and determine the efficiency of the system. The power losses in the filter inductor can seriously decrease the overall efficiency of the converter's system. It's very important to be investigated and compared power dissipations when off-chip and on-chip filter components are used. Integrated inductors occupied huge silicon area. Therefore is necessary to be estimated which type of inductors is more suitable for the designed dc-dc converter.

This paper presents the investigations results of power losses in filter inductor of monolithic dc-dc converter designed on CMOS  $0.35~\mu m$  technology in buck converter implemented on standard CMOS  $0.35~\mu m$  technology. In Section II are presented the received simulations results with Cadence. This section is divided on two parts. In Section II A are shown the received results for power dissipations in the off-chip

T. Brusev and B. Nikolova are with the Department of Technology and Management of Telecommunication Systems, Faculty of Telecommunications, Technical University of Sofia, Kl. Ohridski 8, 1797 Sofia, Bulgaria, E-mail: brusev@ecad.tu-sofia.bg, bnikol@tu-sofia.bg

M. Hristov is with the Department of Microelectronics, Faculty of Electronic Engineering and Technologies, Technical University of Sofia, Kl. Ohridski 8, 1797 Sofia, Bulgaria, E-mail: mhristov@ecad.tu-sofia.bg

filter inductor. For the investigations are used chip coils of the company Murata. In Section II B are presented power losses when on-chip filter inductors of CMOS 0.35  $\mu$ m process are used. Influence of the low Q-factor of integrated filter inductor over the dc-dc converter efficiency is evaluated.

#### II. POWER LOSSES IN OFF-CHIP AND ON-CHIP INDUCTORS

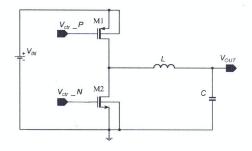

In Fig. 1 is shown the circuit of a buck converter implemented on standard CMOS 0.35- $\mu$ m technology. For the power losses investigation of off-chip and onchip filter inductors an input voltage of 3.6V is chosen for the converter, since this is the normal voltage for Lithium-Ion battery cell that is typically used in battery-powered devices. The output voltage  $V_{out}$  is regulated to 1.2V, which on the other hand is determined by the standard supply voltages of advanced CMOS processes.

FIG. 1. SYNCHRONEOUS BUCK CONVERTER SCHEMATIC.

Part of the total power losses in the monolithic switching mode buck dc-dc converter are due to the series resistance and parasitic capacitance of the filter inductor. Integrated inductors have high series resistance, which grow up with increasing of the inductor's value. This lead to the low quality factor Q of these components [2]. Integration of a spiral inductor with sufficient inductance is not feasible, because they occupy huge silicon area and have low Q factor. The total power dissipated in filter inductor, assuming that the inductor parasitic impedance scale linearly with the inductance is equal to [3]:

$$P_{ind} = b \left[ \frac{I^2}{\Delta i_L f_s} + \frac{\Delta i_L}{3 f_s} + \frac{C_{L0} V_{DD1}^2}{R_{L0} \Delta i_L} \right]$$

(3)

where b is a coefficient depending from the parasitic capacitance and parasitic series resistance of the filter inductor,  $C_{L0}$  and  $R_{L0}$  are respectively the parasitic stray

capacitance and parasitic series resistance per 1 nH inductance,  $V_{DD1}$  is power supply.

The influence of switching frequency  $f_s$  and inductor current ripple  $\Delta i_L$  over the power losses in the filter inductor is investigated. Integrated passive inductors occupied huge silicon area, which make more expensive the electronic devices. It's necessary to be estimated energy dissipation in off-chip and on-chip filter inductors.

Power losses in the filter inductor of the synchroneous buck converter designed on CMOS 0.35-  $\mu$ m technology are analyzed with Cadence, as a function of switching frequency  $f_s$  and inductor current ripple  $\Delta i_L$ . Evaluated and compared are power losses in off-chip and on-chip filter inductor of monolithic buck dc-dc converter.

#### A. Power losses in the off-chip filter inductor

In this section is evaluated power losses in off-chip filter inductors of monolithic dc-dc converter designed on CMOS 0.35-µm technology. The investigated inductors are chip coils for high frequency horizontal wire wound of the company Murata. They have broad range of inductance and high self-resonant frequency. This realizes high Q-factor and stable inductance at high frequency. Their low dc resistance is ideal for low power losses. These off-chip inductors are often used in telecommunication applications.

The received results of power losses in the off-chip filter inductor of buck dc-dc converter are presented below. For the simulations with Cadence on CMOS 0.35-µm technology are used inductor's models of the company Murata [4].

In Table 1 are presented power losses in the offchip filter inductor  $P_{ind}$  as a function of switching frequency  $f_s$  and inductor current ripple  $\Delta i_L$ . Average output current of the buck converter  $I_{out\ (av)}$  equal to 20 mA and  $\Delta i_L = 0.5 \times I_{out\ (av)}$ .

Table 1. Power losses in the off-chip inductors of buck converter;  $\Delta t_L/0.5 x I_{OUT(AV)}$ ;

|                                         | L=10   | L=50  | L=100 | L=200 |

|-----------------------------------------|--------|-------|-------|-------|

|                                         | nΗ     | nΗ    | nH    | nΗ    |

| $I_{out(av)}$ [mA]                      | 20     | 20    | 20    | 20    |

| $f_s$ [MHz]                             | 5000   | 2000  | 1500  | 1000  |

| $\Delta i_L/0.5 \mathrm{x} I_{out(av)}$ | 0.5    | 0.5   | 0.5   | 0.5   |

| $P_{ind}$ [mW]                          | 0.0579 | 0.148 | 0.316 | 1.02  |

In Table 2 are presented power losses in the off-chip filter inductor  $P_{ind}$  as a function of switching frequency  $f_s$  and inductor current ripple  $\Delta i_L$ . Average output current of the buck converter  $I_{out(av)}$  equal to 20 mA and  $\Delta i_L = I_{out(av)}$ .

In Table 3 are presented power losses in the off-chip filter inductor  $P_{ind}$  as a function of switching frequency  $f_s$  and inductor current ripple  $\Delta i_L$ . Average output current of the buck converter  $I_{out\,(av)}$  equal to 20 mA and

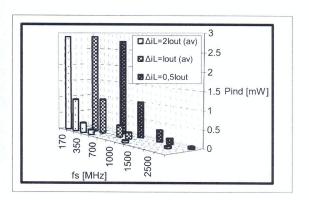

$\Delta i_L = 2 x I_{out~(av)}$ . Received simulations results for power losses in the off-chip filter inductor  $P_{ind}$  of buck converter implemented on CMOS 0.35- $\mu$ m technology as a function of  $f_s$  and  $\Delta i_L$ , for  $I_{out~(av)} = 20$  mA given in Table 1, Table 2 and Table 3, are graphically presented in Fig. 2. For simulations the inductor's models of the company Murata are used.

Table 2. Power losses in the off-chip inductors of Buck converter;  $\Delta I_L/I_{OUT(A\Gamma)}$

|                            | L=10  | L=50  | L=100 | L=200 |

|----------------------------|-------|-------|-------|-------|

|                            | nΗ    | nH    | nΗ    | nH    |

| $I_{out(av)}$ [mA]         | 20    | 20    | 20    | 20    |

| $f_s$ [MHz]                | 2500  | 1000  | 750   | 500   |

| $\Delta i_L/I_{out\ (av)}$ | 1     | 1     | 1     | 1     |

| $P_{ind}$ [mW]             | 0.056 | 0.183 | 0.333 | 1.02  |

Table 3. Power losses in the off-chip inductors of Buck converter;  $\Delta \it{I}_{\it{L}}/2x\it{I}_{\it{OUT}(AU)}$

|                            | L=10  | L=50  | L=100 | L=200 |

|----------------------------|-------|-------|-------|-------|

|                            | nH    | nH    | nΗ    | nΗ    |

| $I_{out(av)}[\mathrm{mA}]$ | 20    | 20    | 20    | 20    |

| $f_s$ [MHz]                | 1250  | 500   | 350   | 250   |

| $\Delta i_L/2xI_{out(av)}$ | 2     | 2     | 2     | 2     |

| $P_{ind}$ [mW]             | 0.062 | 0.139 | 0.291 | 0.97  |

Fig. 2. Power losses in the off-chip filter inductor of buck converter implemented on CMOS 0.35- $\mu$ m technology as a function of  $f_s$  and  $\exists i_L$ , for  $I_{OUT(AU)}$ =20 mA.

Power losses in the off-chip filter inductor of buck dc-dc converter decreased with increasing of switching frequency  $f_s$  and inductor current ripple  $\Delta i_l$ .

#### B. Power losses in the on-chip filter inductor

The dependence of the power dissipation in on-chip filter inductors of CMOS 0.35-µm technology are investigated and evaluated. Standard monolithic inductors are not optimized for the specific applications. In the other hand theirs number of values are limited. That's way is necessary to be designed integrated

inductors with desired value and geometry. One of the Cadence tools named "Virtuoso Passive Component Designer" is used for the extraction of inductor's model parameters [5].

| Colpored Sebag | System (sp. | 60 10      |        |              |         |                 |

|----------------|-------------|------------|--------|--------------|---------|-----------------|

| Type           |             | 994        |        | Coding Print |         | Manager Charles |

| F. Steph book  |             | 1.000      |        | (eder        |         |                 |

| 280 et al. (1) | WW          | Ottograv   |        | Cone         |         |                 |

| C Sproots To   | ntone       | 2000       |        |              |         |                 |

| Acquirige 5    | anthree.    |            |        |              |         |                 |

|                |             |            |        |              |         |                 |

| Service Forons | 194         |            |        | Seekia Court | 4 30000 |                 |

| 5,000 0000     | 100         | Table Same | Sec. 1 | 7            |         |                 |

|                |             |            |        |              |         |                 |

| \$ 5000        |             |            | 1019   |              |         |                 |

| \$ 580         |             |            |        |              |         |                 |

| 1.35           |             |            |        |              |         |                 |

| 5 200          | 3065        |            |        |              |         |                 |

| \$ 81.50       |             |            | 287    | 8            |         |                 |

| 5 116          |             |            |        |              |         |                 |

| 1 4 8          | Careron     |            | 1489   |              |         |                 |

| 8 AC           |             |            | 0.84   |              |         |                 |

| 4.00           | Lend        |            | 132    | 45           |         |                 |

| 13. vec        | Nete        | 0.500      | 2004   | 41           | Safes   |                 |

|                |             | . 5009     | 2.54   |              |         |                 |

FIG. 3. WINDOW FROM CADENCE TOOL "VIRTUOSO PASSIVE COMPONENT DESIGNER".

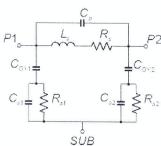

The model of on-chip inductors used in the investigations is shown in Fig. 4. The parameters presented in Fig. 4 are:  $L_s$  – series inductance;  $R_s$  – series resistance;  $C_p$  – parallel capacitance;  $C_{OXI/2}$  – oxide capacitance;  $C_{sI/2}$  – substrate capacitance;  $R_{sI/2}$  – substrate resistance.

The values of the extracted parameters are used for simulations. The received results of power losses in the on-chip filter inductor of buck dc-dc converter are presented below. Investigations are made for average output current of the buck converter  $I_{out\ (av)}$  equal to 20 mA.

FIG. 4. THE MODEL OF ON-CHIP INDUCTORS.

In Table 4 are presented power losses in the on-chip filter inductor  $P_{ind}$  as a function of switchnig frequency  $f_s$  and inductor current ripple  $\Delta i_L$ , for  $\Delta i_L$ =0.5x $I_{out\ (av)}$ .

In Table 5 are presented power losses in the on-chip filter inductor  $P_{ind}$  as a function of switching frequency  $f_s$  and inductor current ripple  $\Delta i_L$ . Average output current of the buck converter  $I_{out\ (av)}$  equal to 20 mA and  $\Delta i_L = I_{out\ (av)}$ .

In Table 6 are presented power losses in the on-chip filter inductor  $P_{ind}$  as a function of switching frequency  $f_s$  and inductor current ripple  $\Delta i_L$ . Average output

current of the buck converter  $I_{out (av)}$  equal to 20 mA and  $\Delta i_L = 2xI_{out (av)}$ .

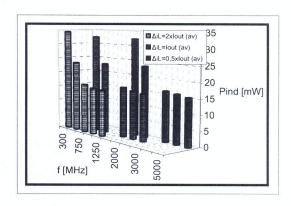

Received simulations results for power losses in the on-chip filter inductor  $P_{ind}$  of buck converter implemented on CMOS 0.35- $\mu$ m technology as a function of  $f_s$  and  $\Delta i_L$ , for  $I_{out\ (av)}$ =20 mA given in Table 4, Table 5 and Table 6, are graphically presented in Fig. 5.

Table 4. Power losses in the on-chip inductors of buck converter;  $\Delta i_L/0.5 x I_{out(ov)}$

|                                         | L=10  | L=14.1 | L=28.2 | L=51  |

|-----------------------------------------|-------|--------|--------|-------|

|                                         | nΗ    | nΗ     | nΗ     | nH    |

| $I_{out(av)}$ [mA]                      | 20    | 20     | 20     | 20    |

| $f_s$ [MHz]                             | 5000  | 4000   | 3000   | 2000  |

| $\Delta i_L/0.5 \mathrm{x} I_{out(av)}$ | 0.5   | 0.5    | 0.5    | 0.5   |

| $P_{ind}$ [mW]                          | 15.37 | 15.9   | 16.35  | 23.59 |

Table 5. Power losses in the on-chip inductors of buck converter;  $\Delta i_L/I_{out\,(av)}$

|                           | L=10  | L=14.1 | L=28.2 | L=51 |

|---------------------------|-------|--------|--------|------|

|                           | nΗ    | nН     | nН     | nH   |

| $I_{out(av)}$ [mA]        | 20    | 20     | 20     | 20   |

| $f_s$ [MHz]               | 2500  | 2000   | 1500   | 1000 |

| $\Delta i_L/I_{out~(av)}$ | 1     | 1      | 1      | 1    |

| $P_{ind}$ [mW]            | 15.37 | 15.74  | 16.37  | 23.6 |

Table 6. Power losses in the on-chip inductors of buck converter;  $\Delta i_L/2xI_{out\,(av)}$

|                               | L=10  | L=14.1 | L=28.2 | L=51  |

|-------------------------------|-------|--------|--------|-------|

|                               | nΗ    | nΗ     | nΗ     | nΗ    |

| $I_{out(av)}$ [mA]            | 20    | 20     | 20     | 20    |

| $f_s$ [MHz]                   | 1250  | 1000   | 750    | 500   |

| $\Delta i_L/2 x I_{out (av)}$ | 2     | 2      | 2      | 2     |

| $P_{ind}$ [mW]                | 15.37 | 15.5   | 16.3   | 23.59 |

Fig. 5. Power losses in the on-chip filter inductor of Buck converter implemented on CMOS 0.35- $\mu$ m Technology as a function of FS and  $\Delta i_L$ , for  $I_{out~(av)}$ =20 mA.

As can be seen from Fig. 2 and Fig. 5 power losses in the filter inductor of buck dc-dc converter goes down with increasing of switching frequency  $f_s$  and inductor current ripple  $\Delta i_L$ . When off-chip filter inductors of the company Murata are used, power dissipation is around 10 times lower compare to the losses in integrated inductors of CMOS 0.35- $\mu$ m process (Fig. 2, Fig. 5). The reason is the high series resistance and low Q-factor of the on-chip inductors.

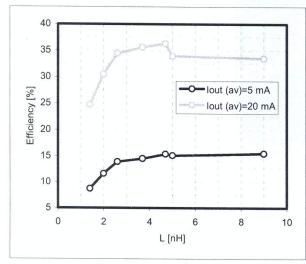

The efficiency of the designed monolithic dc-dc converter as a function of on-chip filter inductors is evaluated. Investigations are made at different average outputs currents ( $I_{out\ (av)}$ ) of the circuit. In Table 7 are shown received results at  $I_{out\ (av)}$ =5 mA. In Table 8 are shown received results at  $I_{out\ (av)}$ =20 mA. The simulation results shown in Table 7 and Table 8 are graphically presented in Fig. 6.

TABLE 7. EFFICIENCY OF THE DC-DC CONVERTER

|                    | L=1.4 | L=2.6 | L=4.7 | L=9  |

|--------------------|-------|-------|-------|------|

|                    | nH    | nH    | nH    | nH   |

| $I_{out(av)}$ [mA] | 5     | 5     | 5     | 5    |

| η [%]              | 8.7   | 13.9  | 15.4  | 15.5 |

TABLE 8. EFFICIENCY OF THE DC-DC CONVERTER

|                    | L=1.4 | L=2.6 | L=4.7 | L=9  |

|--------------------|-------|-------|-------|------|

|                    | nH    | nH    | nH    | nH   |

| $I_{out(av)}$ [mA] | 20    | 20    | 20    | 20   |

| η [%]              | 24.7  | 34.4  | 36.3  | 33.5 |

Fig. 6. Efficiency of the monolithic DC-DC converter designed on CMOS 0.35-µm technology as a function of different on-chip inductors.

The maximum value of the converter's efficiency when on-chip filter inductors are used is 36 %. One of the reasons is low Q-factor of the available integrated inductors.

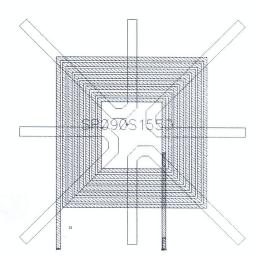

FIG. 7. THE LAYOUT OF ON-CHIP INDUCTORS.

#### III. CONCLUSION

The power losses in the off-chip and on-chip filter inductors of monolithic buck dc-dc converter designed on CMOS 0.35 µm technology has been investigated. When off-chip filter inductors of the company Murata are used, power dissipation is around 10 times lower compare to the losses in integrated inductors of CMOS 0.35-µm process (Fig. 2, Fig. 5). The received results show that by increasing of switching frequency  $f_s$  of the circuit power dissipations in the filter inductor decreased. By increasing of the  $\Delta i_L$  requirements for the inductor's value decreased for fixed switching frequency  $f_s$ . This reduces the parasitic impedance of the filter inductor and the related power loss. A higher value of the  $\Delta i_L$  leads to the increasing of rms current through the inductor which causes to the bigger conduction losses in the inductor.

#### ACKNOWLEDGEMENT

This investigation has been carried out in the framework of the research projects № ДТК 02/50/17.12.2009 and № 102 НИ 199-3.

#### REFERENCES

- [1] Kurson V., S. G. Narenda, V. K. De, and E. G. Friedman, "Monolithic DC-DC Converter Analysis and MOSFET Gate Voltage Optimization," *Proceedings of the IEEE International Symposium on Quality Electronic Design*, pp. 279-284, March 2003.

- [2] Gardner D., A. M. Crawford, S. Wang, "High Efficiency (GHz) and Low Resistance Integrated Inductors Using Magnetic Materials," *Proceedings of the IEEE International Interconnect Technology Conference*, pp. 101-103, June 2001.

[3] Kurson V., "Supply and Threshold Voltage Scalind Techniques in CMOS Circuits", 2004.

- [4] http://www.murata.com

- [5] http://www.cadence.com