# Power supply circuits for mobile wireless applications

### Tihomir S. Brusev

Wireless battery-powered portable electronic devices give opportunity to the people to have faster communication with each other. The increased functionality of mobile phones enables large data packages to be transmitted in the real time. Decreasing of power losses in the electronic building blocks of the transmitter will increase the battery life and system run-time. Power amplifier (PA) is the most energy consuming block. In this paper are considered various power supply circuit architectures suitable for portable electronic devices. Buck dc-dc converter using Pulse-Width Modulation (PWM) designed on CMOS 0.35 µm process is presented. The power losses in the output switching transistors, filter inductor and filter capacitor and evaluated. The efficiency performance of the converter as function of switching frequency  $f_s$  and inductor current ripple  $\Delta i_L$  is investigated. The received results show that maximum efficiency can be achieved if  $\Delta i_L$  is twice higher than average output current of the dc-dc converter. Switching-mode dc-dc converters are discussed in terms of applications in the fourth generation Long-Term Evolution (4G LTE) wireless communications standard. Two-phase interleaved buck dc-dc converter is designed on CMOS 0.35 µm technology. The effect of decreased output current ripple compare to single-phase buck dc-dc converter is demonstrated. The received results demonstrate that two-phase dc-dc converters are appropriate choice for LTE applications, when a high frequency envelope signal has to be tracked.

Захранващи схеми за мобилни безжични приложения (Тихомир Брусев). Преносимите безжични устройства захранвани от батерия дават възможност за по-бърза комуникация между хората. Увеличените функционални способности на мобилните телефони позволяват предаване на големи пакети от данни в реално време. Намаляването на загубите на мощност в изграждащите електронни блокове води до увеличаване на живота на батерията. Мощният усилвател е най-енергоемкия блок в предавателя. В тази статия са разгледани различни захранващи схеми подходящи за преносими електронни устройства. Представена е схема на преобразувател на постоянно напрежение в постоянно (ППН), управляван с широчинноимпулсната модулация (ШИМ), проектирана на CMOS 0.35 µт технология. Изследвани са загубите на мощност в изходните транзистори, филтриращите бобина L и кондензатор С, както и влиянието на честотата на превключване  $f_s$ , и амплитудата на променливата съставка на тока протичащ през бобината  $\Delta i_L$  върху коефициента на полезно действие к.п.д. на преобразувателя. Проектиран е двуфазен преобразувател на ППН на CMOS 0.35 µт технология. Демонстриран е ефектът на намаляване на амплитудата на променливата съставка на изходния ток при двуфазния преобразувател, в сравнение с еднофазния. Получените резултати представени в статията показват, че двуфазния преобразувател на ППН е подходящ за LTE приложения.

#### Introduction

The rapid development of the telecommunication and the microelectronics technologies in the last twenty years changes substantially the human life. The sizes of the integrated circuits (IC) scale in the range of nanometers [1], [2], [3]. Therefore, large number of transistors could be integrated in the small silicon area, which allows the operation frequencies of the building electronic blocks to be in the range of several GHz [4]. On the other hand increasing of the

number of transistor per unit area and frequency of operation of the electronic building blocks leads to increased power consumption of the integrated electronic circuits [5]. Battery-powered portable electronic devices with small sizes and volumes become very popular in the market. The mobile telecommunication devices have developed rapidly. In the nineties and in the beginning of the new century, only voice and text messages could be transferred. Today, except those opportunities, the mobile phones

could be used for high data information transfer [6]. The customers can watch TV programs on their smart phones; they can have fast web browsing; large data packages could be transferred. telecommunication technologies have been used during the years. One of the great challenges for the designer remains how to use much more effectively energy from the battery. The costumers have stringent requirements for long operation time of their mobile devices between two recharges of the battery. The lithium-ion batteries, with standard nominal voltage of 3.6 V, are established as the best battery choice for portable telecommunication devices during the years. They have the energy density more than two times higher compare to the nickel-cadmium battery [7]. The tendency in the market of the mobile phones in the beginning of the century has been decreasing of their sizes and volumes [8]. During that time GSM telecommunication standard have been Switching-mode dc-dc converters were the choice for power supply circuits, which have to deliver the energy to power amplifier of the transmitter [9]. The advantage of those types of circuits is their high efficiency performance while converting battery voltage to desire output dc voltage level. The efforts of the designers in all over the world were focused on decreasing the size of the whole dc-dc converter system in order to satisfy customer demands [10]. One of the goals has been connected with integration of whole dc-dc converter system, including all the components of the low-pass filter, respectively filter inductor and filter capacitor.

Nowadays mobile phones can perform more and more function, as the new wireless communications standard 4G LTE is appeared. The spectrum is used much more effectively in LTE standard [11]. The customer demands follow the increased functionalities and possibilities of the smart phones. Today the sizes of the mobile electronic devices became larger, which allows increasing of the battery dimensions. Nevertheless, run-time period of the whole system is small and should be increased. New types of power supply circuits, which have to ensure the desire energy of transmitter's power amplifier, have to be used [6]. The standard switching-mode converter cannot fulfill requirements to deliver appropriate dynamically changeable output voltage to drain or collector, respectively of MOS or BJT RF transistor of PA. The aim of this paper is to present the received investigation results of power supply circuits for mobile wireless applications designed on CMOS 0.35 µm technology.

# Switching-mode dc-dc converters

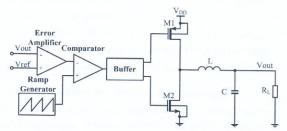

Historically, switching-mode dc-dc converters have been a suitable choice for power supply circuits delivering the required voltage to the transmitter's PA of the wireless portable electronic devices. Those types of converter can exhibit theoretically efficiency  $\eta$  of 100% [12], [13]. Due to the power losses in the building circuit's components, the real integrated dcdc converters can indicate efficiency  $\eta$  values close or greater than 90%. The switching-mode converters have the ability to achieve higher efficiency  $\eta$ compared to linear regulators, especially when the difference between input and output voltage is large [12]. The monolithic buck regulators are in the great interest, because of down scaling tendency in the standard CMOS process technology. In Fig.1 is shown switching mode buck dc-dc converter using PWM control technique.

Fig.1. Switching-mode buck dc-dc converter system using PWM control.

The system illustrated in Fig.1 is designed with Cadence on CMOS 0.35  $\mu$ m process. The power stage of the buck converter includes the output PMOS and NMOS transistors (respectively M1 and M2), filter inductor L and filter capacitor C. The load resistor  $R_L$  represents the current load of transmitter's PA. The control circuit, which performs PWM control of buck dc-dc converter, includes several stages. The stages are respectively error amplifier, ramp generator, comparator and buffer.

## Power losses in buck converter

In order to save battery energy and to increase the system run-time of the portable electronic devices, the power losses in the converter's building blocks have to be minimized. The efficiency of the buck converter system can be expressed by:

(1)

$$h = \frac{P_{out}}{P_{out} + P_{losses}},$$

where  $P_{out}$  is the output power of the dc-dc converter;  $P_{losses}$  are overall power losses in the buck converter system. One of the highest power losses source in the

system are observed in the output MOS transistors MI and M2. Those losses can be divided into conduction and switching power losses [14]:

$$(2) P_{loss,MOS} = P_{sw} + P_{cond},$$

The switching losses in turn are equal to [6]:

(3)

$$P_{sw} = f_s . C_{tot} . V_{DD}^{2}$$

,

where  $C_{tot}$  is the input total capacitance of the MOS transistors,  $f_s$  is the switching frequency of the buck converter,  $V_{DD}$  is the power supply. The conduction losses can be calculated by [14]:

(4)

$$P_{cond} = I_{source}^{2} . r_{on,p} + I_{\sin k}^{2} . r_{on,n}$$

,

where  $I_{source}$  and  $I_{sink}$  are respectively sourcing and sinking current of the MOS transistor, while  $r_{on,p}$  and  $r_{on,n}$  are on-resistance of PMOS and NMOS transistors. The total power losses in MOS transistor can be further expressed by [15]:

(5)

$$P_{tot,MOS} = a \sqrt{\left(I^2 + \frac{\Delta i_L^2}{3}\right) f_s},$$

where  $\Delta i_L$  is the inductor current ripple, I is a dc current supplied to the load, and a is a coefficient depending from equivalent series resistance of the transistors,  $C_{tot}$ , and  $V_{DD}$ . The other losses in the buck dc-dc converter are in the filter inductor L. The total power dissipated in filter inductor, assuming that the inductor parasitic impedance scale linearly with the inductance is equal to [15]:

(6)

$$P_{ind} = b \left[ \frac{I^2}{\Delta i_L f_s} + \frac{\Delta i_L}{3 f_s} + \frac{C_{L0} V_{DD}^2}{R_{L0} \Delta i_L} \right],$$

where b is a coefficient depending on the parasitic capacitance and parasitic series resistance of the filter inductor,  $C_{L0}$  and  $R_{L0}$  are respectively the parasitic stray capacitance and parasitic series resistance per 1nH inductance. Another contributor of the losses in the power stage of the converter system is the filter capacitor C. Those losses are caused by the effective series resistance of the capacitance  $R_C$ . If monolithic capacitor is implemented utilizing the gate oxide capacitance of a MOS transistor, the total power dissipation of filter capacitor is equal to [15]:

$$(7) P_{cap} = d.f_s.Di_L,$$

where d is a coefficient depending on the technology, effective series resistance of the filter capacitor for MOS transistor with channel width equal to 1 $\mu$ m, gait

oxide capacitance, and on channel length of the MOS transistor.

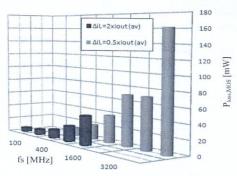

The high  $f_s$  is the key parameter, which allows integration of the passive filter components of buck dc-dc converter [12]. The influence of the  $f_s$  and  $\Delta i_L$ over the losses in the whole designed system is evaluated below. The supply voltage  $V_{DD}$  is chosen to be 3.6 V, which a standard output voltage of lithiumion battery. The investigations are made when the dc output voltage of the converter is regulated to be 1.3 V. The average value of the output current in this particular case is 22 mA. In Fig.2 is presented the dependence of power losses in the output MOS transistors M1 and M2 as a function of  $f_s$  and  $\Delta i_L$ . The figure shows that the power losses in the MOS transistors increase with  $f_s$  and  $\Delta i_L$ . The reason is that the MOS losses are proportion to  $f_s$  and  $\Delta i_L$ , as shown by (5).

Fig.2. The dependence of power losses in the output MOS transistors M1 and M2 as a function of  $f_s$  and  $\Delta i_L$ .

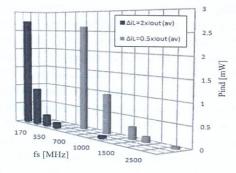

In Fig.3 is presented the dependence of power losses in filter inductor L as a function of  $f_s$  and  $\Delta i_L$ . The results are obtained when an off-chip inductor model is used in simulation. As it can be seen from Fig.2 and Fig.3, the power losses in the buck dc-dc converter are mainly determined by the filter inductor at low  $f_s$  and  $\Delta i_L$ . With increasing  $f_s$  and  $\Delta i_L$ , the inductance value decrease, and thus the dissipation in the parasitic components is lower. On the other hand, the power losses in the MOS transistors go up with increasing  $f_s$ . In a particular area of change of the  $f_s$ and  $\Delta i_L$ , the power losses in the filter inductor dominate in the buck dc-dc converter. In this region with increasing of  $f_s$  and  $\Delta i_L$ , the total power losses in the converter decreases. There is a optimum value of the  $f_s$  and  $\Delta i_L$  at which the efficiency of the buck dc-dc converter has a maximum. When the maximum efficiency of buck dc-dc converter is reached, the power losses in the MOS transistors begin to dominate. Further increase of  $f_s$  u  $\Delta i_L$  leads to lower converter efficiency. The power losses in the filter capacitor C as function of  $f_s$  u  $\Delta i_L$  are presented in

Fig.4. As can be seen, the filter capacitor losses are smaller compare to those in the output MOS transistors and the filter inductor.

Fig.3. Dependence of power losses in the off-chip filter inductor as a function of  $f_s$  and  $\Delta i_L$ .

The power losses  $P_{cap}$  goes up with increase of  $f_s$  and  $\Delta i_L$ , which is in accordance with the formula (7).

Fig.4. Power losses in the filter capacitor C as a function of  $f_s$  u  $\Delta i_L$ .

The design of the PWM control system is focused on the minimization of the current consumption of the different building circuits block. The power losses respectively in the error amplifier, ramp generator, comparator and buffer are considerably small compare to the losses in the power stage.

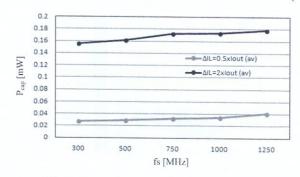

### Efficiency investigation of buck converter

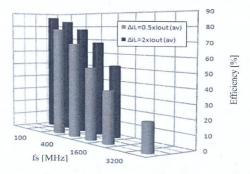

The efficiency of the designed buck dc-dc converter system presented in Fig.1 is investigated below. The output voltage of converter for this analysis is regulated to 1.3V, and then the effect of the  $f_s$  and  $\Delta i_L$  is evaluated. The results are presented in Fig.5. The investigations show that maximum efficiency results can be achieved if  $\Delta i_L$  is twice higher than average output current of the dc-dc converter. In this case the circuit operates at the boundary between discontinues and continuous mode. The main transistor in the power stage of the buck converter is switched-on at zero current. Therefore, the power losses are decreased, which improves the

overall system efficiency. On the other hand, an increase of  $f_s$ , which is desirable for filter's inductor integration, leads to increased switching losses in the output MOS transistors. As can be seen from Fig.5, the efficiency of the buck converter degrades at higher values of  $f_s$ .

Fig.5. Efficiency of the switching-mode buck dc-dc converter system as function of  $f_s$  and  $\Delta i_L$ .

# Power supply circuits for LTE applications Envelope tracking power amplifier system

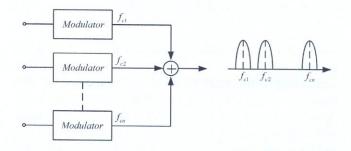

Fig.6. Block circuit diagram of OFDM modulation.

In the LTE standard an orthogonal frequency division multiplexing (OFDM) modulation is used. The information is transferred using several subcarrier frequencies. Signals with different amplitude and phase are summed in the output of the system [11]. Fig.6 shows a block circuit diagram, which illustrates the basic principles of OFDM modulation. The output signal has big amplitude variation. Therefore in order to prevent distortion of the transmitted information, the power amplifier should be linear. The linearity of transmitter's PA is highly desirable for LTE applications, because it helps to avoid interference with nearby users. The big disadvantage of linear PAs is that those circuits have low efficiency performance. The next important feature of the LTE wireless communication standard is that PAs have to work with very high peak to average power ratio (PAPR) [6]. Therefore in the most of time PA has to work in the back-off mode of operation. This leads to further unacceptable degradation of the linear PA's efficiency, if constant supply voltage is used. The linear power amplifier consumes equal dc energy for large and low input signal. Its maximum efficiency can be achieved if output power of the PA is high. The efficiency of the PA  $\eta_{PA}$  can be expressed by formula:

(8)

$$\eta_{PA} = \frac{P_{out}}{P_{DC}},$$

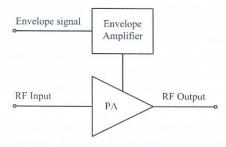

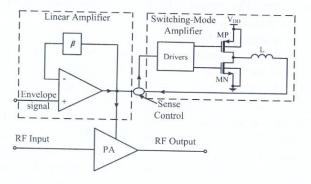

where  $P_{out}$  is a output RF power of PA,  $P_{DC}$  is a dc power delivered to PA. The most promising and used technique for PA's efficiency improvement is envelope tracking [16], [17]. The block diagram of envelope tracking power amplifier (ETPA) system is shown in Fig.7. The envelope amplifier shown in Fig.7 is power supply circuit, which supplies dynamically changeable voltage to the RF transistors of the power amplifier.

Fig.7. Block diagram of ETPA system.

The envelope amplifier tracks the PA input signal and controls the PA supply voltage according the envelope of this signal. In this way, the output voltage of envelope amplifier is regulated to be close to the envelope of the signal and the overall efficiency  $\eta_{ETPA}$  of ETPA system is improved. This parameter can be calculated using formula [16]:

(9)

$$\eta_{ETPA} = \eta_{EA} \eta_{PA},$$

where  $\eta_{EA}$  is the efficiency of the envelope amplifier;  $\eta_{PA}$  is respectively the efficiency of the PA.

### Hybrid envelope amplifier architectures

In the LTE communication standard envelope amplifier has to have fast tracking speed performance, because envelope frequency is high. The standard PWM controlled switching-mode dc-dc converters, used in GSM application, cannot fulfill this requirement. The  $f_s$  of the dc-dc converter have to be to be 5 to 10 times higher than the bandwidth of the LTE signal, if only switching-mode converter is used as an envelope amplifier [18]. In this case the  $f_s$  will

be at least higher than 100 MHz, which is going to increase to unacceptable values power losses in the converter. The result will be a degradation of the overall efficiency of the ETPA system.

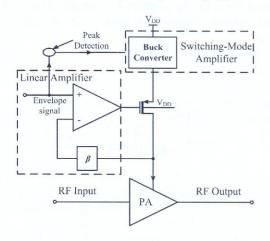

In practice, a hybrid combination between linear amplifier and switching-mode amplifier are used to perform the function of envelope amplifier [6], [11]. [14]. The main idea is that a switching-mode amplifier delivers the low-frequency signal content and the dc voltage, while linear amplifier supplies the high frequency signals to the transmitter's PA. In Fig.8 is illustrated a series combined hybrid architecture composed by a switching-mode buck dc-dc converter and a linear amplifier [19]. The linear amplifier in the combined series hybrid envelope amplifiers architectures should filter output ripples generated from buck converter. All the noises coming from envelope amplifier to the PA will be mixed with the transmitted signal, which will results to a distortion of the transferred data. The drawback is that for high fs the linear amplifier has a low power supply rejection ratio (PSRR) [6]. Also, the entire power delivered to the PA goes through power MOS transistor of the switching-mode amplifier. Therefore switching power losses will be increased especially for high  $f_s$ .

Fig.8. Series combined switching and linear regulator topology of envelope amplifier.

The block circuit of parallel combined hybrid architecture is shown in Fig.9. The switching-mode amplifier is used to deliver average power to PA. The linear amplifier has to deliver the remaining part of the power to PA, when switching regulator cannot respond quickly. The most of the envelope powers have low frequency, which means that the biggest part of the energy is delivered by the high efficient switching-mode stage. This leads to increasing of overall efficiency of the ETPA system. The low efficient linear amplifier delivers only small part,

between 20% and 30%, of the all necessary energy of the PA [20].

Fig.9. Parallel combined switching and linear regulator topology of envelope amplifier.

# Multiphase switching-mode amplifiers

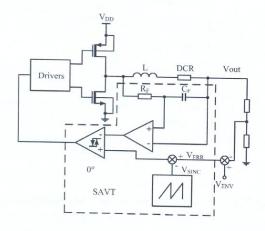

Multiphase switching-mode amplifiers are an alternative of hybrid envelope amplifier used as a power supply circuits for LTE applications. In these architectures low efficient linear amplifier is completely removed. Thus overall efficiency of the ETPA system could be increased. Synchronized adaptive voltage tracking (SAVT) control of two-phased buck dc-dc converter is proposed in [18]. The block circuit diagram of first stage is illustrated in Fig.10.

Fig.10. SAVT control of the two-phased interleaved converter [18].

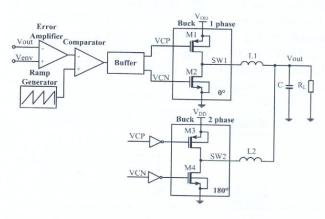

The  $f_s$  and the phase of the two sub-converters are synchronized in the implemented hysteresis control in the proposed method. Thus the spectrum of the inevitable switching noises going to power amplifier could be predicted. The two-phased interleaved buck dc-dc converter is designed and investigated on CMOS 0.35  $\mu$ m process. The block circuit diagram of the switching-mode amplifier's architecture is

presented in Fig.11. The analyzed multiphase converter used PWM control technique. The LTE envelope signal is applied to the negative input of the error amplifier, while the output voltage of the two-phased converter is applied to the positive input. The control signals of the main MOS transistors of the both power buck stages are  $180^{\circ}$  phase shifted. The two-phase converter operates at high switching frequency  $f_s$ , equal to 76 MHz. The supply voltage  $V_{DD}$  is equal to 3.6 V. Output filter inductors L1 and L2 of the both power buck stages are equal to 125 nH. The filter capacitor C is equal to 5 pF. The average value of the output voltage of the converter is regulated to be equal to 1.5 V.

Fig.11. PWM controlled two-phased interleaved buck dc-dc converter designed on CMOS 0.35 µm process.

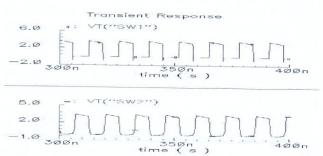

The load resistance  $R_L$  of the two-phase converter represents the current load of RF PA. A source signal with sinusoidal waveform is used in simulations for LTE envelope. The frequency of this sinusoidal signal is equal to 20 MHz. The sinusoidal signal emulates fast changing LTE envelope and it is used in this simulations as a test signal to evaluate the tracking speed of the buck converter. The output voltage signals VT("SW1") and VT("SW2"), respectively of the first and second buck sub-converter stages are presented in Fig. 12. The simulation demonstrate the synchronization operation in the both sub-converter stages. As it can be seen from the figure, the two voltages are 180° phase sifted. Each sub-converter operates at  $f_s$  equal to 76 MHz.

The multiphase dc-dc converter architecture helps for reducing of the output current ripple  $\Delta i_{out}$  of the circuit. The reason is that the phase shifted inductor current ripples  $\Delta i_{Ll}$  and  $\Delta i_{L2}$ , respectively of the first and second sub-converter stage, are summed at the output. The output current ripple  $\Delta i_{out}$  of the two-phase buck converter with non-coupled inductors can be expressed by [21]:

(10)

$$\Delta i_{out} = \frac{V_{out}}{L} (1 - 2D) T_s,$$

where D is duty cycle of the converter,  $T_s$  is switching period of converter, L is the value of filter inductors (if L1=L2, which is the case of the investigated dc-dc converter architecture).

Fig.12. Waveforms of output voltage signals VT("SW1") and VT("SW2").

According to (10) minimum values of  $\Delta i_{out}$  can be received if duty cycle of the converter D is close to 0.5. The inductor current ripples  $\Delta i_L$  of the single-phase and two-phase interleaved buck converter with non-coupled inductors have equal values, and can be expressed by [21]:

(11)

$$\Delta i_L = \frac{V_{out}}{L} (1 - D) T_s,$$

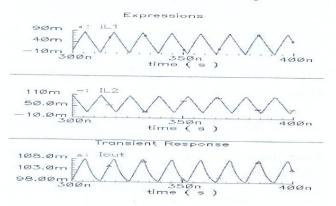

The waveforms respectively of  $\Delta i_{L1}$ ,  $\Delta i_{L2}$  and  $\Delta i_{out}$  of two-phase converter are presented in Fig. 13.

Fig.13. Waveforms of  $\Delta i_{L1}$ ,  $\Delta i_{L2}$ ; and  $\Delta i_{out}$  of two-phase buck dc-dc converter.

The investigations are made when the average value of the output voltage of the two-phase converter is equal to 1.5 V. The obtained results show that:  $\Delta i_{LI}$  is equal to 88.4 mA;  $\Delta i_{L2}$  is equal to 83.14 mA, and  $\Delta i_{out}$  is equal to 9.2 mA. The average value of the output current of the two-phase buck dc-dc converter

is equal to 100 mA. The results show that  $\Delta i_{out}$  is decreased around 9 times than  $\Delta i_{L1}$  and  $\Delta i_{L2}$ , for these particular output parameters of the designed two-phase converter.

|                   |          |                              |                       |                       | Table 1                |                   |  |

|-------------------|----------|------------------------------|-----------------------|-----------------------|------------------------|-------------------|--|

| buck<br>converter | Eff. [%] | I <sub>out(av)</sub><br>[mA] | $\Delta i_{out}$ [mA] | $\Delta V_{out}$ [mV] | P <sub>PMOS</sub> [mW] | P <sub>NMOS</sub> |  |

| single<br>phase   | 71       | 50                           | 9.2                   | 308                   | 3.78                   | 11                |  |

| two-<br>phase     | 70.9     | 100                          | 9.2                   | 132                   | 4.1                    | 10.9              |  |

Table 1 presents the obtained simulation results of single-phase and two-phase buck converters investigated at equal conditions. The values of filter inductors of two circuits are equal to 125 nH, the filter capacitors are equal to 5 pF,  $f_s$  is equal to 76 MHz. The average values of the output voltages of the converters are equal to 1.5 V. The average value of load current of the two-phased dc-dc converter is two times higher than the single-phase circuit. The simulations show that  $\Delta i_{out}$  of the two converters have equal values, while output voltage ripple  $\Delta V_{out}$  of single-phase converter is more than twice higher than  $\Delta V_{out}$  of two-phase converter. Ideally, the ratio could be even higher if the two-phase converter operates near D=0.5. If the single-phase converter should deliver the same output voltage ripples, the output capacitance C should be significantly increased, which would impact negatively the tracking speed of the converter. If a reduction of tracking speed is not acceptable, the large ripples should be compensated by a linear amplifier, which on the other hand would degrade system efficiency.

### Conclusion

In this paper are considered different power supply circuit's architectures suitable for portable electronic devices. PWM controlled buck dc-dc converter designed on CMOS 0.35 µm process is presented. The power losses in the output switching transistors, filter inductor and capacitor and evaluated. Efficiency performance of the converter as function of  $f_s$  and  $\Delta i_L$ is investigated. The obtained results show that maximum efficiency is achieved when  $\Delta i_L$  is twice higher than average output current of the dc-dc converter. A two-phase buck dc-dc converter is designed on CMOS 0.35 µm technology. The effect of decreased  $\Delta i_{out}$  compared to single-phase converter is demonstrated. The results demonstrate that two-phase dc-dc converters are appropriate choice for LTE applications, when a high frequency envelope signal has to be tracked.

### Acknowledgements

The research described in this paper was carried out within the framework of Project  $151\Pi P0011 - 07 - 03.2015$ .

### REFERENCES

- [1] Iwai, H. Future of nano CMOS technology. 2014 IEEE International Conference on Electron Devices and Solid-State Circuits (EDSSC), 18-20 June 2014, pp. 1-3.

- [2] Durand, C., F. Casset, B. Legrand, M. Faucher, P. Renaux, D. Mercier, D. Renaud, D. Dutartre, E. Ollier, P. Ancey, L. Buchaillot. Characterization of IN-IC integrable in-plane nanometer scale resonators fabricated by a silicon on nothing advanced CMOS technology. IEEE 21st International Conference on Micro Electro Mechanical Systems., Jan. 2008, pp. 1016-1019.

- [3] Bohr, T., Nanotechnology Goals and Challenges for Electronic Applications. IEEE Transactions on Nanotechnology, Volume 1, No. 1, March 2002, pp. 56-62,.

- [4] Borkar S., Design Challenges of Technology Scaling. Micro, IEEE, Volume 19, July/August 1999, pp. 23-29.

- [5] Sery G., S. Borkar., and V. De. Life is CMOS: Why Chase the Life After. Proceedings of the IEEE/ACM Design Automation Conference, June 2002, pp. 78-83.

- [6] Hassan M., L. Larson, V. Leung, and P. Asbeck. A Combined Series-Parallel Hybrid Envelope Amplifier for Envelope Tracking Mobile Terminal RF Power Amplifier Applications. IEEE Journal of Solid-State Circuits, Volume 47, no.5, May 2012, pp. 1185-1198.

- [7] Gonai, T., T. Kiyokawa, H. Yamazaki, M. Goto. Development of the lithium ion battery system for space: report on the result of development of the lithium ion battery system for space. Telecommunications Energy Conference, INTELEC '03. The 25th International, 2003, pp. 234-240.

- [8] Jaeseo Lee, G. Hatcher. Evaluation of Fully-Integrated Switching Regulators for CMOS Process Technologies. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, Volume 15, No.9, pp. 1017-1027, 2007.

- [9] B. Saho and G. Rincon-Mora. An Accurate. Low-Voltage, CMOS Switching Power Supply With Adaptive On-Time Pulse-Frequency Modulation (PFM) Control. IEEE Journal of Solid-State Circuits, Volume 39, No.1, 2004, pp. 3-14.

- [10] Kurson V., S. G. Narenda, V. K. De, and E. G. Friedman. Monolithic DC-DC Converter Analysis and MOSFET Gate Voltage Optimization. Proceedings of the IEEE International Symposium on Quality Electronic Design, March 2003, pp. 279-284.

- [11] Hassan, M. Wideband high efficiency CMOS envelope amplifiers for 4G LTE handset envelope tracking

- RF power amplifiers. University of California, San Diego, 2012.

- [12] Mohan N., J. Undeland, W. Robbins. Power Electronics. JWES, NY, 1989.

- [13] Erickson R. W., D. Maksimovic. Fundamentals of Power Electronics. Kluwer Academic Publishers, 2001.

- [14] J. Ham, H. Jung, H. Kim, W. Lim, D. Heo and Y. Yang1. A CMOS Envelope Tracking Power Amplifier for LTE Mobile Applications. Journal of Semiconductor Technology and Science. Volume 14, No.2, April 2014, pp. 235-245.

- [15] Kurson, V. Supply and Threshold Voltage Scalind Techniques in CMOS Circuits. University of Rochester, NY, 2004.

- [16] Y. Li, J. Lopez, D.Y.C. Lie, K. Chen, S. Wu, Tzu-Yi Yang, Gin-Kou Ma. Circuits and System Design of RF Polar Transmitters Using Envelope-Tracking and SiGe Power Amplifiers for Mobile WiMAX. IEEE Transactions on Circuits and Systems I, Volume 58, No.5, May 2011, pp. 893-90.

- [17] Pinon. V., F. Hasbani, A. Giry, D. Pache, and C. Gamier. A single-chip WCDMA envelope reconstruction LDMOS PA with 130MHz switched-mode power supply. IEEE Int. Solid-State Circuits Conf. (ISSCC), San Francisco, CA, 2008, pp. 564-636.

- [18] Sankman J., M. K. Song, and D. Ma. A 40-MHz 85.8%-Peak-Efficiency Switching-Converter-Only Dual-Phase Envelope Modulator for 2-W 10-MHz LTE Power Amplifier. Symposium on VLSI Circuits Digest of Technical Papers, June 2014.

- [19] Kitchen J. N., C. Chu, S. Kiaei, and B. Bakkaloglu. Combined linear and Δ-modulated switch-mode PA supply modulator for polar transmitters. IEEE Journal of Solid-State Circuits, Volume 44, No. 2, Feb. 2009, pp. 404–413.

- [20] Wang F., D. Kimball, D. Lie, P. Asbeck, L. Larson. A Monolithic High-Efficiency 2.4-GHz 20-dBm SiGe BiCMOS Envelope-Tracking OFDM Power Amplifier. IEEE Journal of Solid-State Circuits, Volume 42, No. 6, June 2007, pp. 1271-1281.

- [21] Lee J. P., H. Cha, D. Shin, K. J. Lee, D. W. Yoo, and J. Y. Yoo. Analysis and Design of Coupled Inductors for Two-Phase Interleaved DC-DC Converters. Journal of Power Electronics, Volume 13, No. 3, May 2013, pp. 339-348.

tel.: 965 35 44

e-mail: brusev@ecad.tu-sofia.bg

Received on: 30.04.2015

PhD. Tihomir S. Brusev - is an assistant Professor at the Department of Technology and Management of Communication Systems, Faculty of Telecommunications, Technical University of Sofia. His interests are in the field of analog and mixed IC, dc-dc converters, power supply circuits, cad systems.